Микросхема КМ1804ИР2

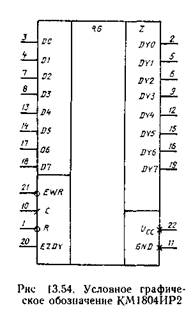

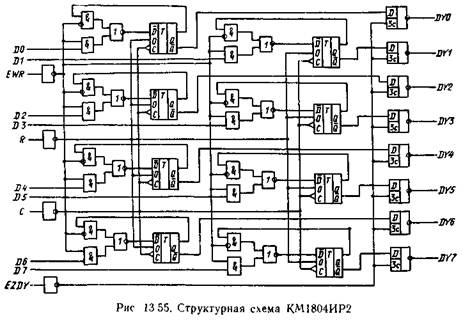

Микросхема КМ1804ИР2 — 8-разрядный параллельный регистр, предназначен для применения в составе центральных процессоров микро-ЭВМ н других вычислительных устройств в качестве универсального регистра (данных, адреса, команд, состояния и т. п.) Допускает неограниченное наращивание разрядности. Условное графическое обозначение микросхемы приведено на рис. 13.54, назначение выводов — в табл. 13.102, структурная схема показана на рис. 13.55, временная диаграмма работы — на рнс. 13.56.

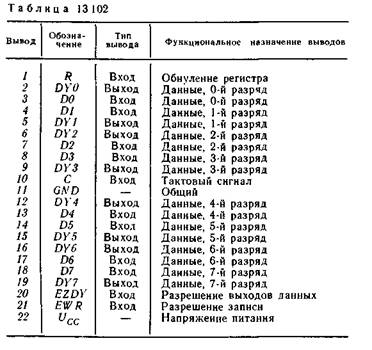

Микросхема КМ1804ИР2 имеет восемь входов данных (D7—DO), вход обнуления регистра (R), вход разрешения записи (EWR), тактовый вход (С), вход разрешения выходов (EZDY) и восемь выходов данных (DY7—DY0).

Микросхема позволяет: записывать информацию, хранить н регенерировать информацию, обнулять записанную информацию.

Синхронизация регистра осуществляется положительным фронтом сигнала, поступающего на тактовый вход С. Выходы данных DY7—DY0 являются выходами на трн состояния. Каждый из восьми разрядов регистра содержит два элемента И, элемент ИЛИ, триггер D-тнпа со входом обнуления и буферную схему с выходом на трн состояния.

Кроме указанных элементов микросхема содержит буферные схемы: тактового сигнала, сигнала обнуления, сигнала разрешения записи и сигнала разрешения выходов.

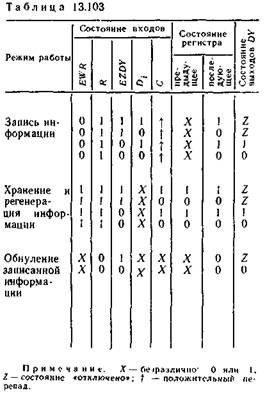

Работа микросхемы осуществляется в соответствии с таблицей истинности (табл. 13.103). Запись информации в регистр производится параллельно со всех восьми входов данных (D7—DO) по положительному фронту тактового сигнала, подаваемого на тактовый вход С, прн наличии сигнала низкого уровня на входе разрешения записи EWRи сигнала высокого уровня на входе обнуления R. Записанная информация передается параллельно на все выходы данных (DY7—DY0) при наличии сигнала низкого уровня на входе разрешения выходов EZDY.

Хранение и регенерация информации осуществляются при наличии сигнала высокого уровня на входе разрешения записи EWRи сигнала высокого уровня на входе обнуления R-

Обнуление информации производится путем подачи на вход обнуления Rсигнала низкого уровня независимо от состояния на других входах микросхемы.

Перевод выводов данных DY7—DY0 в третье состояние не изменяет записанной информации и осуществляется путем подачи на вход разрешения выходов EZDYсигнала высокого уровня.

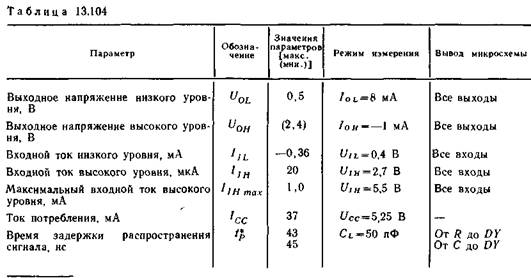

Основные электрические параметры микросхемы приведены в табл. 13.104.

|