Микросхема КМ1804ВС1

Микросхема KMI804BC1 представляет собой 4-разрядную наращиваемую микропроцессорную секцию с высоким быстродействием, предназначенную для применения и составе центральных процессоров микро-ЭВМ, периферийных контроллеров, устройств дискретной автоматики и цифрового управления.

Микросхема имеет:

двухадресную архитектуру внутреннего 16X4 бит регистрового запоминающего устройства;

восемь функции АЛ У (сложение, два вычитания и пять лошческнх функций);

большой выбор пар источников операндов АЛ У;

сдвшп влево,впрано независимо от АЛУ;

четыре флага состояния (перенос, переполнение, нуль п знак).

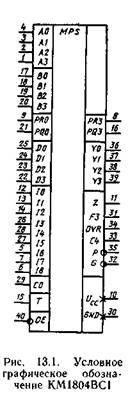

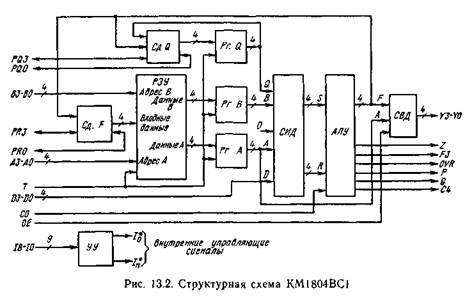

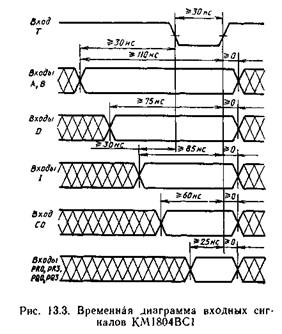

Условное графическое обозначение микросхемы приведено на рис. I3.I, назначение выводов - в табл. )3.2, структурная схема иока->я на па рис. 13.2, временная диаграмма входных сигналов — на рис. 13.3.

В состав микросхемы входят: регистровое ЗУ (РЗУ). селектор источников данных (СИД), арифметико-логическое устройство (АЛУ), селектор выходных данных (СВД), регистры (Рг. А, Рг. В, Рг. Q), сдвнгатели (Сд. Q, Сд. F), устройство управления (УУ).

Любые два слова РЗУ, адресуемые через адресные порты А и б, можно одновременно считывать на соответствующие внутренние

шины данных Л и В. Если адреса А и В совпадают, то на шинах данных А и В появляется одно и то же слово. Регистры Рг. А, Рг. В, стоящие на выходных портах данных А и В РЗУ, пропускают данные, если на вход Т подано напряжение высокого уровня. Если на вход Т подано напряжение низкого уровня, то в регистрах хранятся последние данные, поступившие из РЗУ.

Данные с выхода Сд. Fзаписываются в РЗУ по адресу В при напряжении низкого уровня на входе Т; при высоком уровне на входе Т ячейки РЗУ переводятся в режим хранения/считывания.

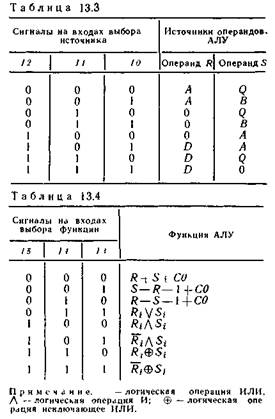

Селектор источников данных предназначен для выбора операндов Rи SАЛУ. Для выбора операндов АЛУ используются входы 12—10 микрокоманды (табл. 13.3).

Арифметико-логическое устройство выполняет три арифметических и пять логических функций над операндами Rи S согласно табл. 13.4.

При наращивании разрядности микросхемы могут соединяться по схеме ускоренного переноса или по схеме с последовательным переносом.

Для организации последовательного переноса в АЛУ имеются вход переноса СО и выход переноса С4. Выходы Р, Gиспользуются при соединении АЛУ микросхем по схеме ускоренного переноса. Остальные выходы (Z, F3, OVR) служат для выдачи результата выполнения функции АЛУ. Выход Z (открытый коллектор) является признаком нулевого результата. Если на выходах FАЛУ все разряды имеют нулевое значение, то на выходе Zустанавливается высокий уровень. Выход F3 соединен со старшим (знаковым) разрядом выхода АЛУ. Выход OVRпоказывает, что результат выполнения арифметической операции выходит за границу разрядности чисел в дополнительном коде

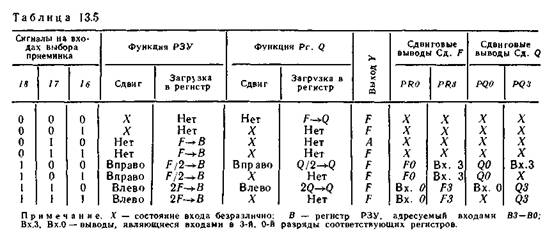

Селектор выходных данных представляет собой двухвходовый коммутатор, который в зависимости от состояния сигналов иа входах 18—16 выдает иа шины Yфункцию АЛУ (F) или выход канала А РЗУ (А) (табл. 13.5). При 0Е—\ выходы селектора Yпереводятся в состояние «отключено».

Результат АЛУ может быть записан в Рг. Qпо положительному фронту тактового сигнала Г при наличии внутренних сигналов разрешения записи, определяемых кодом микрокоманды (см. табл. 13.5). Сдвигатель Сд. Q, стоящий на входе регистра, обеспечивает возможность сдвига его содержимого на одни разряд влево или вправо. Для организации сдвигов содержимого Рг. Qв системе микропроцессорных секций имеются двунаправленные выводы сдвига PQ3, PQ0. Сдвигатель Сд. Qвыполняет только логические сдвиги. Во время сдвига в сторону младших разрядов двунаправленный вывод PQ3 является входом,

a PQO— выходом. При сдвигах в сторону старших разрядов вывод PQ0 является входом, a PQ3—выходом.

Сдвигатель функции АЛУ Сд. Fобеспечивает логический сдвиг вправо (влево) данных перед их записью в РЗУ (см. табл. 13.5). Выводы PR3, PROаналогичны соответствующим выводам PQ3, PQ0 и служат для наращивания разрядности.

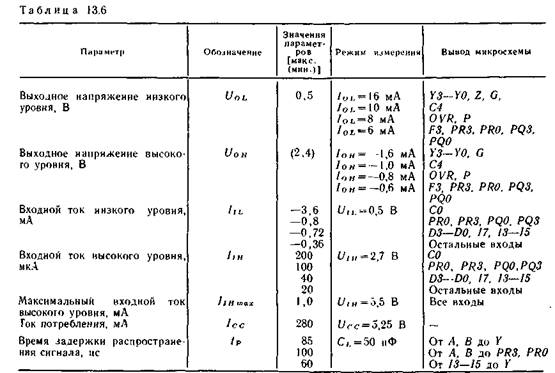

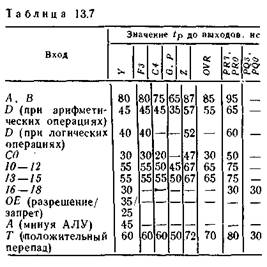

Устройство управления преобразует сигналы на входах выбора микрокоманды 18—10 во внутренние управляющие сигналы I0*—In*. В табл. 13.6 приведены основные электрические параметры микросхемы КМ 1804 ВС 1, в табл. 13.7 — типовые значения динамических параметров. |