Микросхема КМ1804ВС2

Микросхема КМ1804ВС2 представляет собой 4-разрядную наращиваемую микропроцессорную секцию. Она выполняет все функции микропроцессорной секции КМ1804ВС1 и дополнительно ряд функций. Возможность неограниченного наращивания емкости внутренней памяти и трехпортовая трехадресная архитектура, выполнение операций умножения и деления, наличие микрокоманд нормализации чисел, наличие схемы генерации четности, возможность расширения знака чисел обеспечивают большую гибкость применения микросхемы.

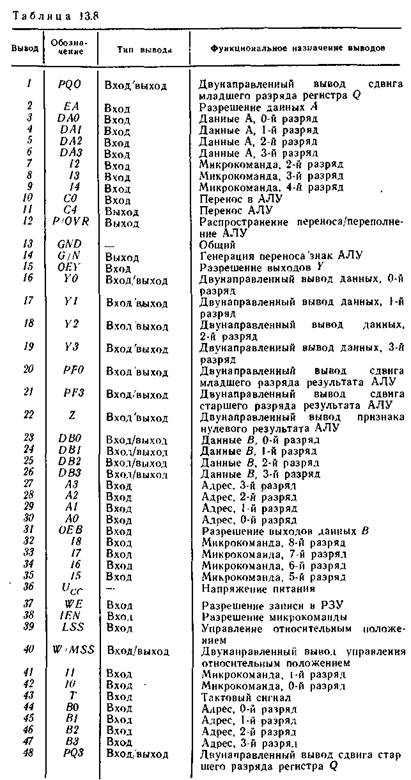

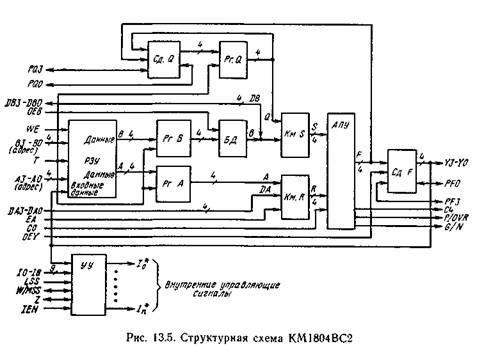

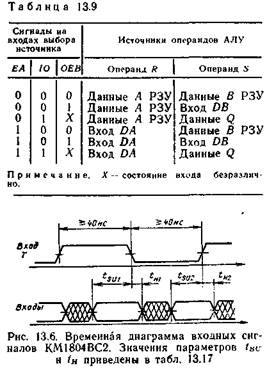

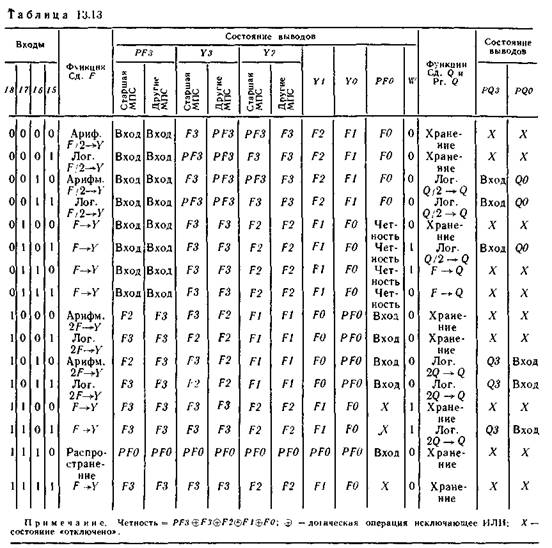

Условное графическое обозначение микросхемы приведено на рис. 13.4, назначение выводов— в табл. 13.8, структурная схема показана иа рис. 13.5, временная диаграмма работы — на рис. 13.6.

В состав микросхемы КМ1804ВС2 в основном входят те же блоки, что и в состав КМ1804ВС1, только сдвигатель Сд. Fрасположен между АЛУ и выходами Y3—Y0 с целью уменьшения времени выполнения операции умножения.

Работу РЗУ необходимо рассматривать совместно с работой регистров Рг. А, Рг. В и буфером данных (БД). Любые два слова РЗУ, адресуемые через адресные порты А и В, можно одновременно считывать на соответствующие внутренние шины данных А и В. Если адреса А и В совпадают, то иа шинах данных А и В появляется одно и то же слово. Регистры Рг. А, Рг. В, стоящие на выходных портах данных А и В РЗУ, пропускают данные, если на вход Т подано напряжение высокого уровня. Если же на вход Т подано напряжение низкого уровня, то в регистрах хранятся последние данные, поступившие из РЗУ. Данные В могут быть прочитаны на двунаправленных выводах DB, если на вход ОЕВ подано напряжение низкого уровня.

Внешние данные записываются в РЗУ по адресу В с двунаправленных К-выводов или с выходных шин Сд. F, если на входы WEи Т одновременно подано напряжение низкого уровня.

АЛУ может выполнять семь арифметических и девять логических операций над двумя 4-разрядными операндами. Коммутаторы Км. S, Км. Rиа входах АЛУ обеспечивают возможность выбора источников операндоз АЛУ. В зависимости от состояния входа ЕА коммутатор Км. Rвыбирает либо шину DAвнешних данных, либо данные А РЗУ в качестве одного из источников операнда АЛУ. Сигналы на входах ОЕВ и 10 управляют работой Км. S, который выбирает либо данные В РЗУ, либо входы DB, либо содержимое Рг. Qв качестве другого источника операнда АЛУ. Таким образом, АЛУ может работать с данными от двух внешних источников, либо от одного внутреннего и одного внешнего источника, либо от двух внутренних источников. В табл. 13.9 приведены все возможные пары источников операндов АЛУ.

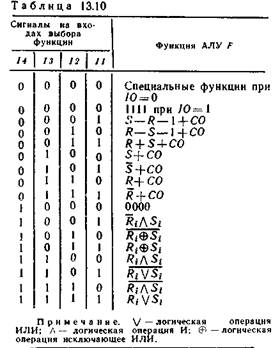

Стандартные функции, выполняемые АЛУ, определяются состоянием входов микрокоманды 11—14 н приведены в табл. 13.10.

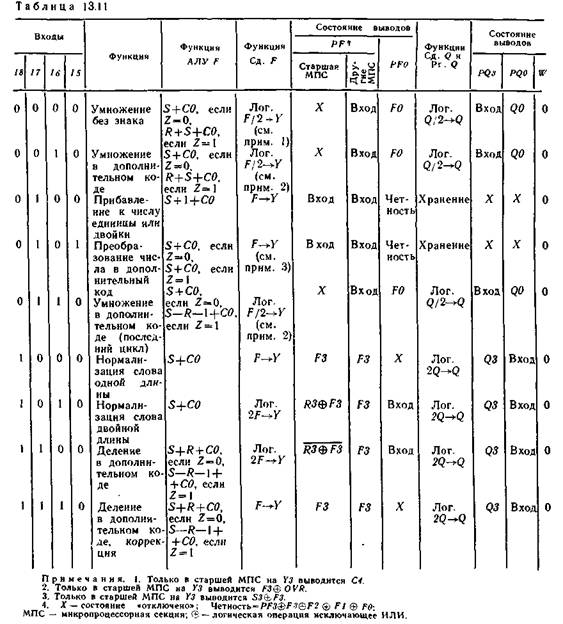

Если на входы 10—14 подано напряжение низкого уровня, то микросхема выполняет специальные функции, определяемые состоянием входов микрокоманды 15—18 (табл. 13.11).

При наращивании разрядности микросхемы могут соединяться по схеме ускоренного переноса или по схеме последовательного переноса. Для организации последовательного переноса в АЛУ имеются вход переноса СО н выход переноса С4.

Выходы GIN, P/OVRиспользуются при соединении АЛУ микросхем по схеме ускоренного переноса. При этом в зависимости от относительного положения микропроцессорной секции (АШС) в младшей и средней МПС выходы GJN, P/OVRявляются выходами сигналов ускоренного переноса (генерации Gи рас пространения Р переноса), а в старшей МПС данные выходы используются как знаковый Л' и переполнения OVR. Выход N — обычно старший разряд результата операции, используется для определения знака результата АЛУ.

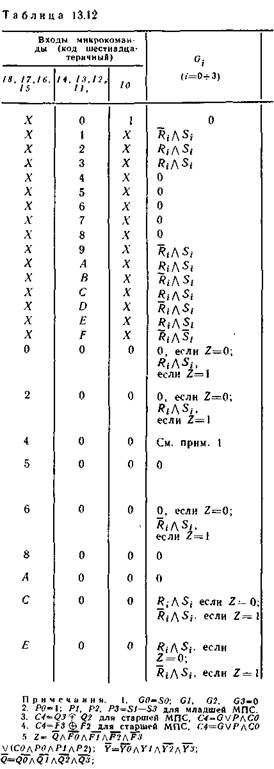

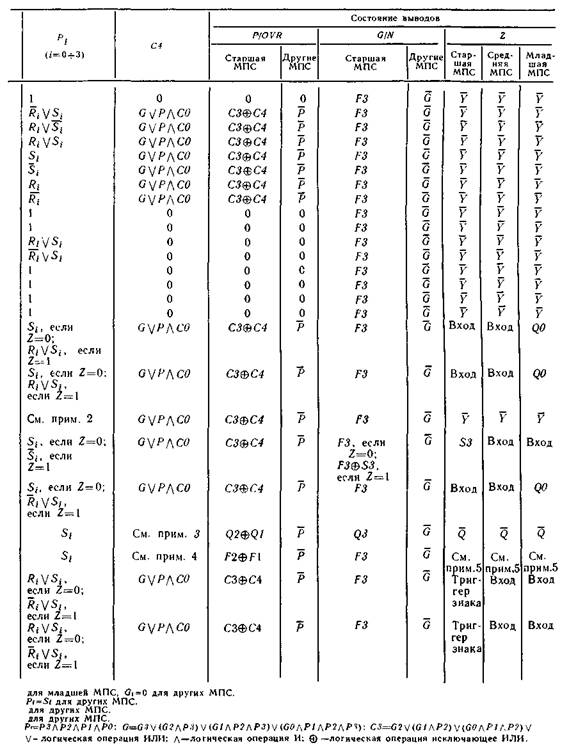

Выход OVRпоказывает, что результат выполнения арифметической операции выходит за границу разрядности чисел в дополнительном коде. В табл. 13.12 приведены логические выражения сигналов состояния в зависимости от выполняемой операции АЛУ. В зависимости от состояния входов микрокоманды 15—18 сдвигатель Сд. Fпропускает результат АЛУ Fна выход либо без сдвига, либо со сдвигом влево или вправо. В микро схеме предусмотрена возможность осуществлять логические и арифметические сдвиги. При арифметических сдвигах разряды сдвигаются в обход старшего (знакового) разряда результата операции АЛУ в старшей МПС, а при логических сдвигах старший разряд сдвигается вместе с остальными разрядами. Во время сдвигов в сторону младших разрядов двунаправленный вывод PF3 обычно является входом, а вывод PF0 — выходом. При сдвигах в сторону старших разрядов вывод PF3 обычно является выходом, а вывод PF0 — входом.

Сдвигатель Сд. Fтакже имеет возможность распространения знака на все разряды результата АЛУ. Имеется микрокоманда, когда сигнал на входе PF0 (знаковый) передается на выходы Y0—Y3 и PF3.

На некоторых микрокомандах Сд. Fгенерирует сигнал контроля четности результата АЛУ с учетом сигнала на входе PF3. Данный

сигнал выводится на выход PF0. Возможность контроля четности в микросхеме обеспечивает обнаружение ошибок АЛУ. Выходы Сд. Fпредставляют собой ТТЛ-веитили с тремя состояниями. Работой этих вентилей управляет вход разрешения У выводов OEY. Если на вход OEYподано напряжение низкого уровня, то двунаправленные выводы Yработают как выходы Сд. F. Если же на вход OEYподано напряжение высокого уровня, то выводы У работают как входы РЗУ. В табл. 13.11 и 13.13 приведены операции, выполняемые сдвигателем Сд. F. Работу регистра Рг. Qрассмотрим совместно с работой Сд. Q. Обычно Рг. Qпредназначен для использования в операциях деления и умножения, однако его можно применять как накопительный регистр общего назначения. Результат АЛУ может быть записан в Рг. Q по положительному фронту тактового сигнала Т при наличии внутренних сигналов разрешения записи, определяемых кодом микрокоманды. Сдвигатель Сд. Q, стоящий на входе регистра, обеспечивает возможность сдвига его содержимого на один разряд влево или вправо. Для организации сдвигов содержимого Рг. Q в системе МПС имеются двунаправленные выводы сдвига PQ0 и PQ3, Сдвигатель Сд. Qвыполняет только логические сдвиги. Во время сдвигов в сторону младших разрядов двунаправленный вывод PQ3 является входом, а вывод PQ0 — выходом. При сдвигах в сторону старших разрядов вывод PQ3 является выходом, а вывод PQ0 — входом.

Микросхема обеспечивает возможность арифметических и логических сдвигов двойной длины. Для осуществления этих сдвигов необ ходимо соединить вывод PQ3 старшей МПС с выводом PF0 младшей МПС. Сдвиг двойной длины осуществляется микросхемой, если на входы управления подана микрокоманда, на которой происходит одновременный сдвиг результата АЛУ и содержимого Рг. Q. В табл. 13.11 и 13.13 приведены функции Рг. Qи Сд. Q, выполняемые ими в зависимости от состояния входов микрокоманды 15—18.

Устройство управления представляет собой комбинационную схему и предназначено для преобразования внешних сигналов управления (10—18, IEN, LSS, W/MSS, Z) во внутренние сигналы управления(/п—In). Входы 10—18 являются входами микрокоманды. В зависимости от значений логических сигналов на этих входах выбирается конкретная микрокоманда, выполняемая микросхемой согласно табл. 13.9—13.13. С помощью входа LSSи двунаправленного вывода WJMSSможно запрограммировать место расположения каждой секции в многоразрядном устройстве обработки данных. Если на вход LSSподано напряжение низкого уровня, то микросхема программируется как младшая МПС и двунаправленный вывод W/MSSработает как выход W. При соединении данного двунаправленного вывода W/MSSс входом WE(в младшей МПС) происходит запрет записи данных

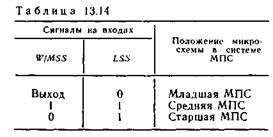

в РЗУ на некоторых микрокомандах, когда W=l (см. табл. 13.11 и 13.13). Если же иа вход LSSподано напряжение высокого уровня, то двунаправленный вывод W/MSSстановится входом. Микросхема программируетсякак старшая МПС, если на вход MSSподано напряжение низкого уровня, и как средняя МПС, если на вход MSSподано напряжение высокого уровня. Программирование места расположения каждой секции в многоразрядном устройстве представлено в табл. 13.14.

Двунаправленный вывод Zпризнака нулевого результата АЛУ используется как выход с открытым коллектором и показывает, что при выполнении АЛУ некоторой функции получен нулевой результат. Данный вывод может быть объединен между различными МПС по схеме монтажное ИЛИ. При выполнении микросхемой специальной функции «деление» (см. табл. 13.11, 13.12) вывод Zв старшей МПС является выходом триггера сравнения знака. Триггер сравнения знака предназначен для правильного выполнения операции «Выравииваиие делителя».

По положительному фронту тактового сигнала Т в триггер сравнения знаков записывается инверсная сумма по модулю 2 текущего значения старшего разряда делителя со старшим разрядом делителя предыдущего цикла. На некоторых специальных функциях вывод Zиспользуется как вход, управляя которым можно изменять функцию АЛУ микросхем (см. табл. 13.11 и 13.12). Если на вход разрешения микрокоманды JENподан

высокий уровень напряжения, то иа выходе разрешения записи данных в РЗУ Wпоявляется напряжение высокого уровня. Триггер сравнения знаков, РЗУ и Pr. Q при этом находятся в режиме хранения.

Таким образом, управляя входом IEN, можно запрещать запись информации во все внутренние регистры микросхемы.

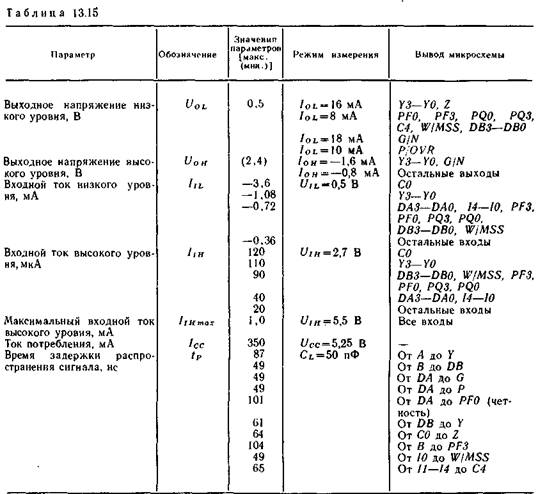

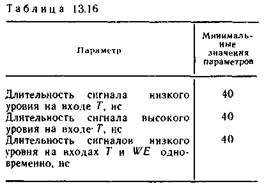

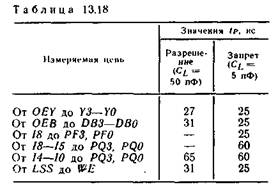

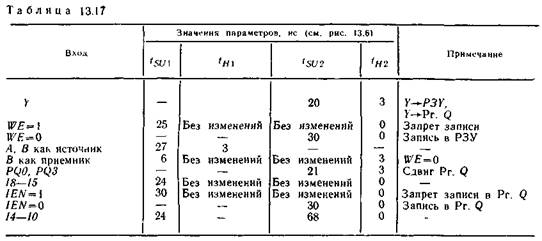

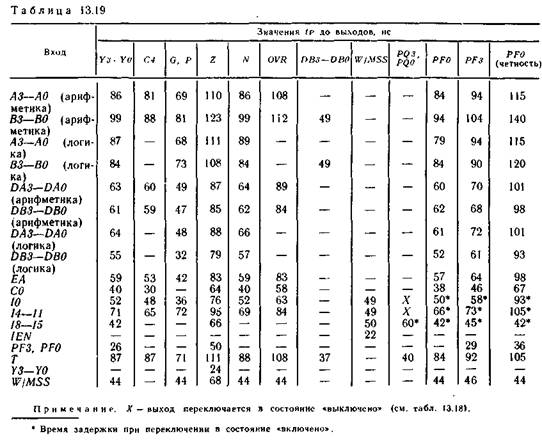

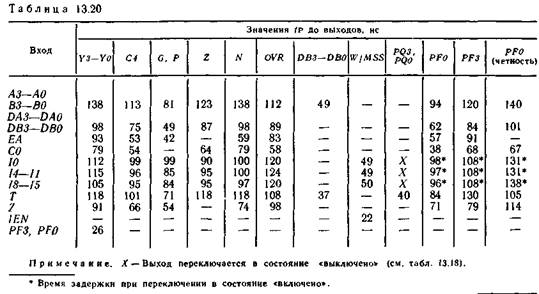

Основные электрические параметры микросхемы КМ1804ВС2 приведены в табл. 13.15, типовые значения динамических параметров — в табл. 13.16, 13.17 (времена подготовки и удержания сигнала), 13.18 (задержки до выходов с тремя состояниями), 13.19 (комбинациоииые задержки для стандартных функций АЛУ) и 13.20 (комбинационные задержки для специальных функций).

|