Микропроцессор серии КМ1813ВЕ1.

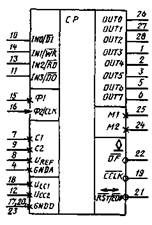

Микросхема КМ1813ВЕ1 представляет собой однокристальную программируемую микро-ЭВМ с аналоговыми устройствами ввода/вывода, предназначенную для цифровой обработки сигналов в реальном масштабе времени. Она может быть использована для замены аналоговых функциональных узлов в системах, работающих в реальном масштабе времени. Набор команд микро-ЭВМ в сочетании с высокой точностью (25 двоичных разрядов) работы АЛУ позволяет строить на ее основе сложные системы цифровой обработки сигналов (ЦОС) и цифрового динамического управления. На микро-ЭВМ К.М1813ВЕ1 реализуются типовые функциональные узлы: фильтры нижних и верхних частот, содержащие до 20 комплексных пар полюсов и (или) нулей (фильтр 40-го порядка); детекторы; выпрямители; ограничители; умножители и делители 25-разрядных двоичных чисел; генераторы колебаний и функции - аппроксимация нелинейных функций, например квадратичных, логарифмических, логические операции; мультипликация входных и выходных сигналов и др. Используя возможности непосредственного цифрового ввода/вывода, несколько К.М1813ВЕ1 могут микросхем серии КН1811 быть объединены в сложные мультипроцессорные системы. Основные области применения: низкочастотная связь, промышленная автоматика, гидроакустика, геофизика, биомедицина, синтез, анализ и распознавание речи и др. Микросхема К.М1813ВЕ1, выполненная по я-МДП- технологии, конструктивно реализована в металлокерамическом корпусе типа 2121.28-6(7) с прозрачной для ультрафиолетового излучения крышкой. Напряжение питания Ucc, = +5 B±5% и Ucc2 =-5 В + 5%. Диапазон рабочих температур от —10 до +70 С. Микросхема имеет два режима функционирования: «Программирование» и «Работа». Условное графическое обозначение микросхемы и назначение выводов в указанных режимах приведены на рис. 1, табл.1 и рис. .2, табл. .2 соответственно.

Общие характеристики КМ1813ВЕ1 |

Способ управления |

Микропрограммный |

Способ синхронизации |

От внешнего или внутреннего генератора |

Разрядность АЛУ |

27 бит |

Разрядность данных |

25 бит |

Объем ППЗУ |

192х24 бит |

Объем ОЗУ |

40х25 бит |

Возможности масштабирования |

22 2-13 |

Разрядность команд |

24 бит |

Объем памяти коэффициентов |

16х4 бит |

Устройства ввода/вывода |

Аналоговые и цифровые |

Число разрядов АЦП и ЦАП |

9 (8 + знак) |

Число каналов ввода |

4 |

Число каналов вывода |

8 |

Таблица 1 |

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

1—3 |

OUT3—OUT5 |

Выходы |

Выходные сигналы в аналоговой и (или) цифровой форме |

4 |

GNDA |

— |

Аналоговый общий |

5, 6 |

0UT6, 0UT7 |

Выходы |

Аналоговые сигналы в аналоговой и (или) цифровой форме |

7 |

С1 |

— |

Для подключения внешнего конденсатора выборки и хранения входного сигнала |

8 |

U RF.F |

— |

Источник опорного напряжения |

9 |

С2 |

— |

Для подключения внешнего конденсатора выборки и хранения входного сигнала |

10 |

JN0/DJ |

Вход |

Входной аналоговый сигнал или цифровой последовательный сигнал (ТТЛ уровень) |

11 |

IN3JD0 |

Вход/выход |

Входной аналоговый сигнал или выходной цифровой последовательный сигнал (открытый сток) |

12 |

Ucc2 |

|

|

|

|

|

Напряжение питания —5 В |

13 |

IN2IRD |

Вход/выход |

Ввод аналогового сигнала или вывод синхроимпульса «Чтение» (открытый сток) |

14 |

IN1/WR |

Вход |

Ввод аналогового сигнала или вывод синхроимпульса «Запись» (открытый сток) |

15, 16 |

Ф1, Ф2С1К |

Входы |

Тактирование схемы |

17, 20, 23 |

GNDD |

— |

Цифровой общий |

18 |

U сс1 |

— |

Напряжение питания +5 В |

19 |

CCLK |

Выход |

Внутренний сигнал синхронизации, частота следования импульсов равна 1/16 частоте следования входных тактовых импульсов (открытый сток) |

21 |

RST/EOP |

Вход/выход |

Напряжение низкого уровня; возвращает счетчик команд в начальное состояние. Как выходной сигнал, оно указывает на присутствие команды ЕОР (открытый сток) |

22 |

OF |

Выход |

Напряжение низкого уровня; указывает на переполнение АЛУ во время предыдущей команды |

24, 25 |

Ml, M2 |

— |

(открытый сток) |

26-28 |

OUT0—OUT2 |

Выходы |

Определяет режим работы входов/выходов Сигналы в аналоговой и (или) цифровой форме |

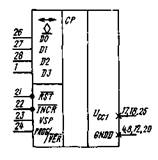

Таблица 2 |

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

1 |

D3 |

Вход/выход |

Запись и чтение информации из ППЗУ (открытый сток) |

4,8, 12, 20 |

GNDD |

— |

Цифровой общий |

17, 18, 25 |

Ucc1 |

|

Напряжение питания +5 В |

21 |

RST |

Вход |

Установка счетчика адреса слов ППЗУ в начальное состояние |

22 |

JNCR |

Вход |

Подача импульсов, изменяющих состояние счетчика адреса слов ППЗУ |

23 |

VSP |

Вход |

Для подключения программирующего напряжения +25 В при записи и +5 В при чтении |

24 |

PROGVER |

Вход |

Управление двунаправленной шиной данных ППЗУ (при чтении ТТЛ низкий уровень) |

26—28 |

D0—D2 |

Вход/ выход |

Запись и чтение информации из ППЗУ (открытый сток) |

|

|

Рис. 1 |

Рис. 2 |

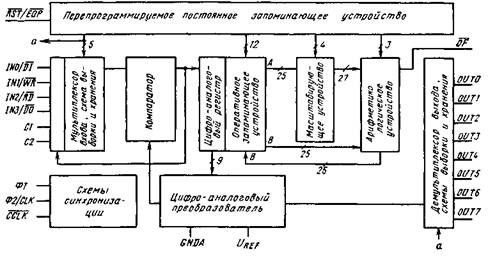

Структурная схема КМ1813ВЕ1 — однокристальной перепрограммируемой микроЭВМ с аналоговыми устройствами ввода/вывода — показана на рис. 3. Программа, записанная в ППЗУ, управляет работой всех функциональных узлов микросхемы. По заданной в ППЗУ программе микросхема выполняет отсчет значения аналогового или цифрового сигнала по одному из четырех входных каналов, производит выборку и запоминание на внутреннем устройстве выборки и хранения, реализует аналого-цифровое преобразование выборки сигнала и передачу ее цифрового представления на цифровой процессор для обработки в соответствии с заданной программой. Результат обработки передается на цифро-аналоговый преобразователь. Аналоговое представление результата обработки через выходной демультиплексор и выходную схему выборки и хранения подается на любой из восьми выходных каналов в соответствии с управляющей программой. Специальный режим позволяет производить непосредственную обработку цифровых сигналов, т. е. без использования каналов аналого-цифрового и цифро-аналогового преобразований. Функционально КМ1813ВЕ1 построена по конвейерному принципу таким образом, что обеспечивает одновременную (параллельную) работу аналоговой и цифровой частей микросхемы. Тем самым обеспечивается высокая производительность выполнения операций (около 2 млн. операций/с) и достигается возможность обработки сигналов в реальном масштабе времени. Цифровая часть микросхемы содержит: перепрограммируемое постоянное запоминающее устройство (ППЗУ), оперативное запоминающее устройство (ОЗУ), двоичное масштабирующее устройство (МУ) и арифметико-логическое устройство (АЛУ). Аналоговая часть схемы содержит: четыре аналоговых входа, входной мультиплексор, схему выборки и хранения (одну на все четыре канала), аналого-цифровой (АЦП) и цифро-аналоговый преобразователи (ЦАП), выходной мультиплексор, восемь выходных каналов со схемами выборки и хранения. Связь между цифровой и аналоговой частями микросхемы осуществляется через специальный регистр (ЦАР - цифро-аналоговый регистр).

|

Рис. 3 |

|

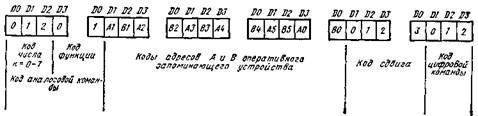

Рис. 4 |

Программная память микросхемы КМ1813ВЕ1 представляет собой ППЗУ с ультрафиолетовым стиранием; ППЗУ содержит 192 командных слова. Командное слово длиной в 24 разряда разбито на пять полей (рис. 4), из которых одно управляет работой аналоговой части микросхемы, остальные четыре - цифровой (ОЗУ МУ, АЛУ).

В режиме «Программирование» 24-разрядное командное слово разбивается на шесть 4-разрядных (D3, D2, Dl, DO) слов. Следовательно, в режиме «Программирование» ППЗУ имеет организацию 1152X4. Распределение 4-разрядных слов в пределах поля команды показано на рис. 4.

В режиме «Работа» производится последовательное считывание содержимого ППЗУ по четыре команды с записью в 96-разрядном буферном регистре. Считывание одной команды буферного регистра производится за четыре такта работы тактового генератора. Счетчик программ возвращается в исходное состояние после выполнения последней, 191-й команды, а также после поступления команды «Конец программы» или «Возврат по условию».

Таблица 3

Мнемоника константы |

Значение констант |

Мнемоника константы |

Значение констант |

Десятичное |

Двоичное |

Десятичное |

Двоичное |

КР0 |

0 |

0,000 |

КМ1 |

—0,125 |

1,111 |

КР1 |

+0,125 |

0,001 |

КМ2 |

—0,150 |

1,110 |

КР2 |

+0,250 |

0,010 |

КМ3 |

—0,375 |

1,101 |

крз |

+0,375 |

0,011 |

КМ4 |

—0,500 |

1,100 |

КР4 |

+0,500 |

0,100 |

КМ5 |

—0,625 |

1,1011 |

КР5 |

+0,625 |

0,101 |

КМ6 |

—0,750 |

1,010 |

КР6 |

+0,750 |

0,110 |

КМ7 |

—0,875 |

1,001 |

КР7 |

+0,875 |

0,111 |

КМ8 |

—1,000 |

1,000 |

Частота выборок сигнала определяется числом команд в программе и временем командного цикла (четыре такта тактового генератора). Оперативное запоминающее устройство выполняет функции памяти данных и памяти констант. Оно представляет собой двухадресное ОЗУ статического типа с произвольной выборкой и записью, организованной как 40 словХ25 разрядов. Расширенное поле адресов ОЗУ (64 слова вместо 40 необходимых) используется для образования констант и организации регистра сопряжения (ЦАР) между аналоговой и цифровой частями микросхемы. ОЗУ имеет два порта: порт А и порт В. По порту А осуществляется только считывание информации, которая передается через МУ на один из входов АЛУ в качестве операнда А. Через порт В информация поступает на второй вход АЛУ в качестве операнда В. Результаты вычислений АЛУ записываются в ОЗУ только по порту В.

Обращение к константам осуществляется через порт Л по 16 старшим адресам поля операнда А (адреса А 11хххх, где А5 = А4=1). Константы соответствуют четырем младшим разрядам кода адреса и как 4-разрядное слово передаются через МУ на вход операнда А АЛУ. Набор значений программируемых констант и соответствующие мнемокоды приведены в табл. 18.3. Номенклатура значений коэффициентов может быть существенно расширена за счет использования масштабирующего устройства.

Цифро-аналоговый регистр имеет длину в девять разрядов и допускает несколько способов обращений. Как ячейка памяти, ЦАР занимает 9 старших разрядов 25-разрядного слова и допускает обращение по порту А и (или) порту В, подобно остальным 40 ячейкам памяти ОЗУ. Выход ЦАР подключен непосредственно ко входам ЦАП. Кроме того, ЦАР (9 разрядов) используется как регистр последовательного приближения при аналого-цифровом преобразовании под управлением поля аналоговой команды. При передаче результата аналого-цифрового преобразования в процессор оставшиеся 16 младших разрядов (25-разрядного слова) устанавливаются в 1, что соответствует переводу результата преобразования в дополнительный код. Могут быть также произведены выборка и контроль любого разряда ЦАР для организации выполнения условных команд АЛУ.

Масштабирующее устройство представляет собой арифметический двоичный сдвигатель, расположенный между выходом порта А ОЗУ и входом операнда А АЛУ. Это позволяет масштабировать операнд А на любое значение от 22 до 2~13 (сдвиг влево на 2 разряда, сдвиг вправо на 13 разрядов При сдвиге влево освободившиеся правые разряды заполняются нулями, а при сдвиге вправо освободившиеся левые разряды заменяются значениями знакового разряда (дополнительный ход). Подобный сдвиг эквивалентен умножению операнда А на 2* (kпринимает значения от —13 до +2). Мнемокоды сдвига МУ и соответствующие значения эквивалентного умножителя операнда А как множимого приведены в табл. 4.

В АЛУ производятся вычисления в дополнительном коде с 25-разрядной точностью над масштабированным операндом А и операндом В, поступающим из ОЗУ. Результат вычислений записывается в ОЗУ по адресу операнда В. Старший разряд переменной является знаковым, а обычный диапазон переменной х находится в пределах—1,0<х< + 1,0. Минимальное приращение любой переменной при этом составляет б = 2~24 = 5,96-10~8. АЛУ имеет логику для работы при выполнении МУ сдвига влево, а именно в случае переполнения эта логика обеспечивает сохранение знакового разряда. Переполнение возникает в тех случаях, когда результат вычисления выходит за пределы разрядной сетки ОЗУ (25 разрядов). Сдвиг влево является частным случаем переполнения. Для обработки режима переполнения в АЛУ предусмотрено расширение разрядной сетки до 27. При работе без переполнений четыре старшие разряды этой разрядной сетки соответствуют значению знакового разряда. В случае переполнения в 26-й и 27-й разряды записывается результат сдвига влево. Для определения переполнения, т. е. того, что конечный результат вышел за пределы границ —1,0<х<1,0, в АЛУ анализируются знаковые разряды операндов А и В, 26 и 27 разряды АЛУ, а также перенос в знаковый разряд АЛУ.

Для АЛУ могут быть заданы два режима работы с переполнениями: с коррекцией результата и без коррекции результата. В режиме с коррекцией результат заменяется ближайшим максимально допустимым значением переменной с учетом знака ( — 1,0, если переполнение вызвала отрицательная переменная; + 1,0, если переполнение вызвала положительная переменная), и на вывод «Переполнение» выдается сигнал низкого уровня.

В режиме без коррекции результата происходит расширение двоичного значения переменной до 27 разрядов. После выполнения АЛУ соответствующей операции 25 младших разрядов результата вычисления записываются в ОЗУ по адресу операнда в и на выводе «Переполнение» всегда высокий уровень.

Таблица 4

Мнемокод сдвига |

Код операции |

Эквивалентный множитель |

L01 |

1110 |

21= 2,0 |

L02 |

1101 |

22=4,0 |

R00 |

1111 |

20=1,0 |

R01 |

0000 |

2-1=0,5 |

R02 |

0001 |

2-2=0,25 |

R03 |

0010 |

2-3=0,125 |

R04 |

0011 |

2-4=0,625 |

R05 |

0100 |

2-5=0,03125 |

R06 |

0101 |

2-6=0,015625 |

R07 |

0110 |

2-7=0,0078125 |

R08 |

0111 |

2-8=0,00390625 |

R09 |

1000 |

2-9=0,001953125 |

R10 |

1001 |

2-10=0,0009765625 |

R11 |

1010 |

2-11=0>00048828125 |

R12 |

1011 |

2-12=0,000244140625 |

R13 |

1100 |

2-13=0,0001220703125 |

Входные каналы построены на четырех аналоговых ключах выборки с использованием общего внешнего конденсатора хранения. Для обеспечения точности преобразования меньше 1/2 единицы младшего разряда емкость внешнего конденсатора должна быть около 750 пФ. Время выборки должно быть равно примерно 6-кратному значению постоянной времени RC-цепочки схемы выборки и хранения. В микросхеме К.М1813ВЕ1 эта постоянная времени при 750 пФ внешней емкости 750—1000 не. Необходимое время выборки обеспечивается программным путем. При командном цикле 600 не микросхемы КМ1813ВЕ1 для этого требуется последовательность из восьми команд ввода. Для систем с большим временем командного цикла необходимо использовать внешний конденсатор с большой емкостью.

Аналого-цифровое преобразование хранимого схемой выборки и хранения отсчета аналогового сигнала реализуется программным путем в соответствии с алгоритмом последовательного приближения с точностью, соответствующей девяти двоичным разрядам, один из которых используется в качестве знакового. Для программирования используются команды преобразования знакового разряда CVTSи преобразования остальных восьми (* = 7—0) разрядов ЦАР CVT (k). Для полного 9-разрядного преобразования при длительности цикла команд 600 не требуется 34 команды (табл. 18.5). Перед преобразованием необходимо установить нули во всех разрядах ЦАР. Наличие команд типа «Нет операции» NOPобъясняется необходимостью обеспечения паузы в 1,2 мкс на время установления ЦАП после преобразования каждого разряда.

Таблица 5

Номер команд |

Поле аналоговых команд |

Номер команд |

Поле аналоговых команд |

Номер команд |

Поле аналоговых команд |

0 |

/N(k) |

11 |

NOP |

22 |

NOP |

1 |

IN(k) |

12 |

CVT7 |

23 |

NOP |

2 |

IN(k) |

13 |

NOP |

24 |

CVT3 |

3 |

IN(k) |

14 |

NOP |

25 |

NOP |

4 |

IN(k) |

15 |

CVT6 |

26 |

NOP |

5 |

IN(k) |

16 |

NOP |

27 |

CVT2 |

6 |

IN(k) |

17 |

NOP |

28 |

NOP |

7 |

IN(k) |

18 |

CVTS |

29 |

NOP |

8 |

NOP |

19 |

NOP |

30 |

CVT1 |

9 |

CVTS |

20 |

NOP |

31 |

NOP |

10 |

NOP |

21 |

CVT4 |

32 |

NOP |

|

|

|

|

33 |

CVTO |

Цифро-аналоговое преобразование основано на методе поразрядного взвешивания цифрового представления числа, записанного в ЦАР после обработки на процессоре в соответствии с заданной программой. Результат цифро-аналогового преобразования передается на одни из восьми выходных каналов.

Каждый из восьми аналоговых выходных каналов содержит свои схемы выборки и запоминания, демультиплексируемые на буферизированный выход ЦАП. Для обеспечения вывода необходимо соблюдать два правила: на время записи информации в ЦАР выход должен быть отключен; на время установления.

Таблица 5

Цифровая команда

(З разряда) |

Адрес В

(6 разрядов) |

Адрес А

(6 разрядов) |

Код сдвига

(4 разряда) |

Аналоговая команда

(5 разрядов) |

Таблица 6

Управляющие напряжения |

Режим ввода |

Режим вывода |

Ml |

М2 |

+5 В |

+5 В |

1N0 - 1N3 - аналоговые |

OUT0—OUT7 — аналоговые |

+5 В |

-5 В |

D1 — цифровой последовательный |

D0—цифровой последовательный;

OUT0—OUT3—аналоговые;

OUT4 —OUT7—цифровые |

-5 В |

+5 В |

IN0—IN3 — аналоговые |

OUT0—OUT3—цифровые:

OUT4—OUT7 —аналоговые |

—5 В |

-5 В |

1N0—1N3 -аналоговые |

OUT0—OUT7—цифровые |

ЦАП должны быть использованы три команды NOP, а на время установления выходной схемы выборки и хранения — еще несколько команд «Вывод» OUT (к) общей длительностью 4,2—4,8 мкс.

Входные и выходные каналы микросхемы могут быть использованы для передачи по иим аналоговых и цифровых сигналов. Установка режимов для ввода и вывода производится по управляющим выводам Mlи М2, на которые подаются напряжения —5 и +5 В в различных сочетаниях. Выводы Mlи М2 не могут быть использованы для динамического переключения режимов ввода и вывода. Возможные режимы ввода и вывода при различных сочетаниях Mlи М2 приведены в табл. 18.6. В режиме Ml = +5 В, М2=—5 В происходит блокировка входных аналоговых устройств микросхемы и обеспечивается непосредственный последовательный ввод н вывод цифровой информации через регистр ЦАР. Для организации ввода/вывода в этом режиме используются четыре входных канала.

Последовательный ввод осуществляется по командам CVTSи CVT (к) в такой последовательности: знак, старший разряд ЦАР, младшие разряды ЦАР (s, к = 7—0). При этом по каналу DIинверсно вводится цифровая информация за исключением знакового разряда. Одновременно в течение выполнения команды CVT (к) на канал RDподается синхроимпульс низкого уровня.

Последовательный выход осуществляется по команде OUT (к) от старшего к младшему разряду регистра ЦАР. _При этом из какого разряда ЦАР по каналу DOинверсию выводится цифрован информация. Одновременно в течение выполнения команды OUT (k) на канал WRподается синхроимпульс низкого уровня. Уровни сигналов по входу и выходу микросхемы определяются значением внешнего опорного напряжения, которое может находиться в пределах +14-+2 В. При этом уровни входного и выходного напряжений будет находиться в пределах ±Uref, а единица младшего разряда I/bef/256 В. Источник опорного напряжения должен быть тщательно стабилизирован, поскольку любая нестабильность Urefявляется шумом для ЦАП. Для обеспечения на выходе OUT0—OUT7 уровня ТТЛ опорное напряжение должно быть более 1,75 В. В микросхеме КМ1813ВЕ1 для ассемблера используется формат команд, изображенный на рис.5. Систему команд КМ1813ВЕ1 можно разделить на цифровые и аналоговые команды. В свою очередь, группа цифровых команд может быть разделена на безусловные, условные и команды условного перехода. Группа безусловных команд приведена в табл. 7. Операция сложения ADD. Команда формирует сумму чисел операндов В к А после сдвига последнего на kразрядов. Результат записывается по адресу операнда В, т. е. ADDBBBAAAR01 NOP. Эквивалентная операция на языке ФОРТРАН: б = б+А*0,5. Операция вычитания SUB. Команда» реализует сложение числа по адресу AAA, дополненного до 1, с числом по адресу ВВВ, т. е. SUBВВВ КРЗ R00 NOP. Эта операция означает вычитание постоянной величины 0,375 из переменной величины по адресу ВВВ. Операция пересылки LDA. Команда производит засылку числа по адресу AAA, сдвинутого на kразрядов, в ячейку по адресу ВВВ. т. е. LDABBBAAAR01. Операция исключающее ИЛИ XOR. Команда реализует сложение по модулю 2, т. е. XORBBBAAAR00. Операция логического умножения AND. Команда реализует поразрядное логическое умножение одной переменной величины на другую в соответствии с правилом 1-1 = 1, 1-0=0, 0-1=0, 0-0=0, т. е. ANDBBBAAAR00. Операция взятия абсолютной величины ABS. Команда реализует сдвиг числа по адресу AAAна заданное число разрядов, определение абсолютного значения и запись результата по адресу ВВВ, т. е. ABSBBBAAAR00 NOP. Операция ограничения LJM. Команда реализует присвоение максимально допустимого значения числу по адресу В в зависимости от знака числа по адресу А, т. е. если число А положительное, то числу по адресу В присваивается значение +1 (0Л11...1), если же число А отрицательное, то по адресу В получим число—1 (1.000...0). Операция сложения с абсолютным значением ABA. Команда ABAскладывает абсолютное значение операнда AAAс операндом ВВВ. результат записывается по адресу ВВВ. Группы условных команд и команд условного перехода микросхемы КМ1813ВЕ1 приведены в табл. 8 и 9 соответственно. Для организации условных цифровых команд используется команда CND, которая записывается в аналоговом поле формата команды (см. рис. 5). Команда CNDможет принимать вид CND (s), что означает проверку знакового разряда в регистре ЦАР, или вид CND (k), что означает проверку разрядов числа, записанного в регистре ЦАР. Сказанное относится к командам LDACNDи ADDCND.

Таблица 7

Команда |

Код операции |

Число циклов |

Алгоритм |

Описание команды |

ADD |

110 |

1 |

(Ах2N)+В->В |

Сложение |

SUB |

101 |

1 |

B—(AX2N)->B |

Вычитание |

LDA |

111 |

1 |

(Ax2N)->B |

Пересылка |

XOR |

000 |

1 |

(Ax2N)+B-> |

Исключающее ИЛИ |

AND |

001 |

1 |

(Ax2N)× B->B |

Логическое И |

ABS |

011 |

1 |

|(Ax2N)|-> В |

Абсолютная величина |

ABA |

100 |

1 |

|(Ax2N)|+B-> В |

Сложение с абсолютной величиной |

Lim |

010 |

1 |

+1->B, если А≥0,

-1->B, если А<0 |

Ограничение |

В случае SUBCNDимеют место проверка предыдущего значения бита переноса в знаковый разряд АЛУ CYPи запись текущего значения переноса CYв k-й разряд регистра ЦАР. В случае SUBCNDSинверсное значение текущего значения разряда переноса CYзаписывается в знаковый разряд ЦАР. При выполнении безусловных операций LDA, XOR, AND, ABSразряд переноса обнуляется. Команда ABACNDиспользуется для выключения механизма коррекции результата при переполнении АЛУ, а команда XORCND— для включения механизма коррекции. Команды RNZи JNZобеспечивают условный переход на фиксированное место в программе: RNZ— на начало программы, JNZ — на 32 команды вперед. Особенности построения памяти программы определяют необходимость расположения RNZв командном слове, адрес которого делится на 4, т. е. 4, 8, ..., 188. При этом возврат на начало программы по условию происходит после выполнения остальных трех команд четверки. В свою очередь, JNZнеобходимо записывать в командном слове, занимающем третий адрес в четверке, а переход по условию на 32 команды вперед происходит после выполнения последующих пяти команд. |