Микросхемы КР580ВК28 и КР580ВК38

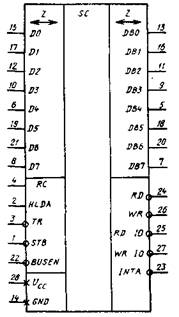

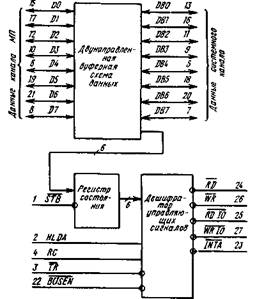

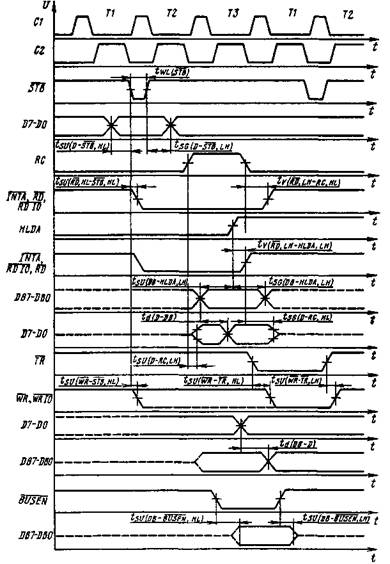

Микросхемы КР580ВК28, КР580ВК38 системный контроллер и буферный регистр данных, применяются в микропроцессорных системах на базе микропроцессора КР580ВМ80А для формирования управляющих сигналов и как буферный регистр данных. Условное графическое обозначение микросхем приведено на рис. 1, назначение выводов — в табл. 1, структурная схема показана на рис. 2, временные диаграммы на рис. 3. Микросхемы КР580ВК38 и КР580ВК28 отличаются лишь длительностью двух формируемых управляющих сигналов: WRи WRI0. Системный контроллер формирует управляющие сигналы по сигналам состояния микропроцессора при обращении к ЗУ: RDи WR, при обращении к УВВ: RD10 и WRЮ, INTA, а также обеспечивает прием и передачу 8-разрядиой информации между каналом данных микропроцессора по выводам D7—DOн системным каналом по выводам DB7—DB0-истемный контроллер состоит из двунаправленной буферной схемы данных, регистра состояния и дешифратора управляющих сигналов.

Восьмиразрядная параллельная трехстабильная буферная схема данных принимает информацию с канала данных микропроцессора по выводам D7—D0 и передает в регистр состояния информацию состояния, на системный канал данных по выводам DB7DB0 выдает данные в цикле записи по сигналу fW. В цикле чтения по сигналу RCбуферная схема принимает данные с системного канала по выводам DB7 и DB0 и передает по выводам D7—D0 на канал данных микропроцессору. Регистр состояния по входному сигналу STBфиксирует информацию состояния микропроцессора в такте 77 каждого машинного цикла микропроцессора.

Рис.1

Таблица 1

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

1 |

STB |

Вход |

Стробирующий сигнал состояния |

2 |

HLDA |

Вход |

Подтверждение захвата |

3 |

TR |

Вход |

Выдача информации |

4 |

RС |

Вход |

Прием информации |

5, 7, |

B4, DB7 |

Выход/ |

Канал данных системы |

9, 11 |

DB3, DB2, |

ВХОД |

|

13, 16, |

DBO, DB1, |

|

|

18, 20 6, 8, 10, 12,15,17, |

DB5, DB6 D4, D7, D3, D2, DO, D1, |

Вход/ выход |

Канал данных микропроцессора |

19, 21 14 |

D5, D6

GND |

|

Общий |

22 |

BUSEN |

Вход |

Управление передачей данных и выдачей сигналов |

23 |

INTA |

Выход |

Подтверждение запроса прерывания |

24 |

RD |

Выход |

Чтение из ЗУ |

25 |

RD 10 |

Выход |

Чтение из УВВ |

26 |

WR |

Выход |

Запись в ЗУ |

27 |

WR 10 |

Выход |

Запись в УВВ |

28 |

Ucc |

Вход |

Напряжение питания +5В |

Дешифратор управляющих сигналов формирует один из управляющих сигналов в каждом машинном цикле: при чтении ЗУ — RD, при записи в ЗУ — WR, при чтении из УВВ — RD10, при записи в УВВ — WR10, при подтверждении запроса прерывания — сигнал 1NTA. Асинхронный сигнал BUSENуправляет выдачей данных с буферной схемы и управляющих сигналов с дешифратора: при напряжении низкого уровня на входе BUSENбуферная схема передает данные и формируется один из управляющих сигналов; при напряжение высокого уровня все выходы микросхемы переводятся в высокоомное состояние Напряжение высокого уровня на входе HLDAпереводит выходы ~RD, RD10, INTAв пассивное состояние (напряжение высокого уровня) и блокирует передачу информации через буферную схему данных. Управляющие сигналы WRи WR10 формируются в цикле записи в микросхеме КР580ВК28 по сигналу TR, в микросхеме КР580ВК38 — по сигналу STBПри работе с микропроцессором КР580ВМ80А системный контроллер в цикле подтверждения запроса прерывания формирует три сигнала INTAдля приема трех байтов команды CALLот контроллера прерывания КР580ВН59.

Рис.2

Рис.3

В небольших микропроцессорных смете мах выход INTAмикросхем КР580ВК28/КР580ВК38 можно подсоединить к напряжению + 12 В через резистор сопротивлением 1 кОм. Во время действия сигнала RCбуферная схема данных микросхемы формирует код команды RST7 и передает на канал данных микропроцессора. Таким образом, микро схема обеспечивает единственный вектор прерывания с номером 7 без дополнительных компонентов. |