Микросхемы статических ОЗУ

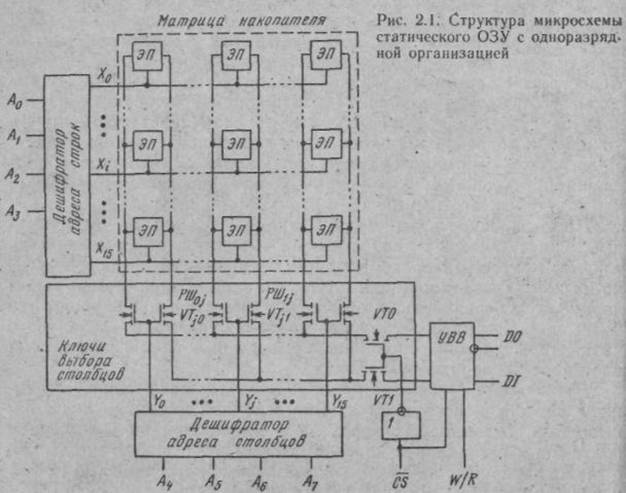

Типичный вариант структурного построения микросхемы статического ОЗУ приведен на рис. 2.1. Для примера выбрана I сравнительно несложная микросхема памяти К56ТРУ2 (564РУ2) с емкостью 256 бит. Условное графическое изображение микро-схемы представлено на рис. 1.5, а. Структурная схема включает выполненные на едином кристалле кремния матрицу накопителя, дешифраторы кода адреса строк Ао — А3 (Ао — младший разряд) и столбцов А4 — А7, ключи выбора столбцов и устройство ввода-вывода (УВВ). Режимом микросхемы управляют сигналы CS (Выбор микросхемы) и W/R (Запись-считывание).

Матрица накопителя содержит 256 ЭП, расположенных на пересечениях 16 строк и 16 столбцов. Каждый ЭП представляет собой статический триггер, который может быть реализован на основе биполярных или МДП-транзисторов. Это зависит от технологии изготовления микросхем. В данном случае микросхема

К561РУ2 изготовлена по КМДП-технологии, поэтому ее основу составляет триггер (рис. 2.2) на МДП-транзисторах дополняющего (комплементарного) типа, имеющих каналы разного типа проводимости: VT1, VT2—каналы n-типа, VT3, VT4 — каналы р-типа. У триггера два парафазных совмещенных входа-выхода. Ключевыми транзисторами VT5, VT6 триггер соединен с разрядными шинами РШ1 РШ0, по которым подводится .к триггеру при записи и отводится от него при считывании информация в парафазной форме представления: PШ=D, РШо = D. Ключевые транзисторы затворами соединены с адресной шиной (строкой). При возбуждении строки сигналом выборки Х=1, снимаемым с выхода дешифратора адреса строк, ключевые транзисторы открываются и подключают входы-выходы триггера к разрядным шинам. При отсутствии сигнала выборки строки, т. е. при Х=0, ключевые транзисторы закрыты и триггер изолирован от разрядных шин. Таким образом реализуют в. матрице режим обращения к ЭП для записи или считывания информации и режим хранения информации.

Для сохранения информации в триггере необходим источник питания, т. е. триггер рассматриваемого типа является энергозависимым. При наличии питания триггер способен сохранять свое состояние сколь угодно долго. В одно из двух состояний, в которых может находиться триггер, его приводят сигналы, поступающие по разрядным шинам в режиме записи: при D=l (РШ, = 1, РШо = 0) VTl, VT4,—открыты, VT2,_ VT3 — закрыты, при D = 0 (РШ|=0, РШо=1) транзисторы свои состояния изменяют на обратные. В режиме считывания РШ находятся в высокоомном состоянии и принимают потенциалы плеч триггера, передавая их затем через устройство ввода-вывода на выход микросхемы DO, DO. При этом хранящаяся в триггере информация не разрушается.

Особенность КМДП-триггеров заключается в том, что в-режиме хранения они потребляют незначительную мощность от источника питания, поскольку в любом- состоянии триггера в той или другой его половине один транзистор, верхний или нижний, закрыт. В режиме обращения, когда переключаются элементы матрицы, дешифраторы и другие функциональные узлы микросхемы, уровень ее энергопотребления возрастает на два-три порядка.

Для обращения к микросхеме для записи 0 или 1 следует подвести эту информацию ко входу DI, подать код адреса А{Ао — А7}, разрешающий сигнал CS и сигнал W/R, соответствующий режиму записи (см. табл. 1.2). При указанных сигналах возбуждается заданная строка X,, выбранная дешифратором

кода адреса строк, и в результате этого открывается доступ поразрядным шинам ко всем ЭП данной строки. Одновременно возбуждается один из выходов Yj дешифратора кода адреса

столбцов и, открывая соответствующие транзисторы VTj0, VTj, в блоке ключей выбора столбца, коммутирует выбранный столбец на УВВ. Доступ к разрядным шинам этого столбца со стороны УВВ обеспечивает сигнал CS=1, открывающий ключи VT0 и VT1. Настройку УВВ на прием сигнала со входа DI осуществляет

сигнал W/R= 1.

Обращение к микросхеме для считывания происходит аналогично, но при значении сигнала W/R = 0.

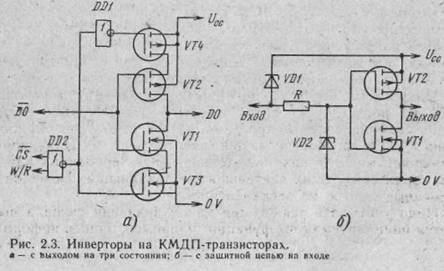

В большинстве микросхем памяти УВВ содержит выходной ключевой усилитель-формирователь, способный принимать три состояния: два функциональных, соответствующих 0 или 1, и одно высокоомное (третье) состояние. В третьем состоянии выход практически отключен от приемника информации, например информационной шины. Пример такого элемента приведен на оис. 2.3, а. Элемент представляет собой инвертор на транзисторах VT1, VT2, дополненный двумя ключевыми транзисторами VT3, VT4, обеспечивающими реализацию третьего состояния выхода. Состоянием ключей управляет сигнал V: при V = 0 оба ключа закрыты и выход находится в высокоомном состоянии, при V=l ключи открыты и схема выполняет свои функции инвертора, передавая на выход DO микросхемы информацию, считанную с выбранного ЭП. Сигнал V формирует внутренняя схема, придавая ему значение, определяемое сигналами CS и W/R: если рассмотренный выход реализован в микросхеме, работающей в соответствии. с табл. 1.2, то V = CS-(-W/R. При наличии еще одного стробирующего выход сигнала ОЕ=0, как у микросхемы КР537РУ8, условие управления выходом запишется в виде: V = CS>W/R + OE или V = CS-W/R-OE.

Наличие у микросхемы выхода на три состояния позволяет соединять информационные вход и выход для подключения их к' единой информационной шине.

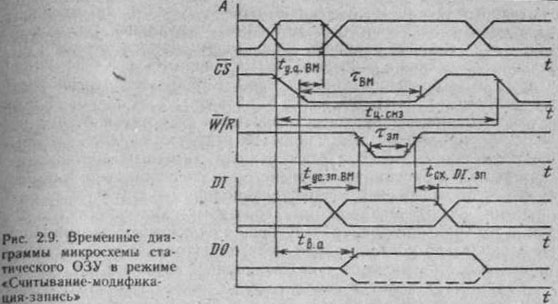

Работу микросхемы статического ОЗУ в динамическом режи

ме иллюстрирует временные диаграммы, представленные на рис.- 1.9. Диаграммы определяют последовательность подачи адресных и управляющих сигналов при записи и считывании, а также временные интервалы между различными сигналами и длительности сигналов: время цикла записи-считывания (-tu.зп.сч), длительность сигналов CS (выбора микросхемы) твм и паузы между ними Твм, время установления сигнала CS относительно адреса tyc.BMa, время сохранения адреса после сигнала GS tcx а. вм. время выборки адреса tB a или время выбора микросхемы te.BM и др.

Следует обратить внимание на требование к форме сигналов управления CS и W/R. В § 1.2 отмечено, что у асинхронных статических ОЗУ эти сигналы могут быть поданы в форме уровней напряжения, соответствующих 0 или I в зависимости от режима, а у тактируемых — в форме импульса, причем требование импульснрго представления относится обычно к сигналу CS.

Микросхема К561РУ2, временные диаграммы которой приведены на рис. 1.9, относится к группе тактируемых. Этой же группе принадлежат микросхемы серии К537, ряд микросхем серии К132 и др. Многие микросхемы статических ОЗУ являются асинхронными. Для них значительная часть временных параметров, характеризующих длительности управляющих сигналов и их временные сдвиги, не регламентирована. Надо учитывать также, при каком значении сигнала выполняется инициируемая им функция: например, запись информации в микросхему К561РУ2 происходит при сигнале W/R=l (см. рис. 1.9), а считывание—при W/R = 0, для микросхемы серии К537 и других серий необходимы обратные значения сигнала W/R при выполнении этих же функций: W/R = 0 при записи, W/R=l при считывании. Указание на активное значение сигнала содержит его обозначение: если есть знак инверсии, то активным значением является 0, если нет, то 1.

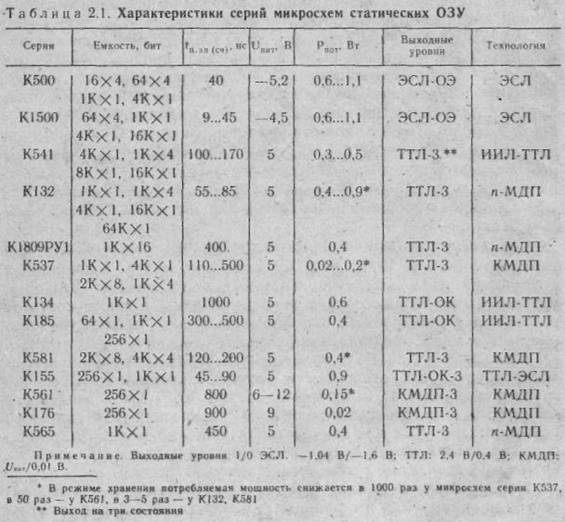

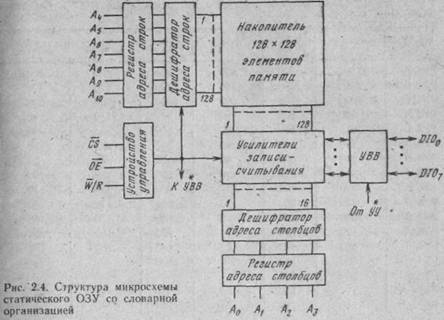

Рассмотренная структурная схема (см. рис. 2.1) представляет собой пример реализации статических ОЗУ с одноразрядной организацией. Этот тип микросхем преобладает в современной номенклатуре микросхем памяти (табл. 2.1). Вместе с тем все более активное развитие получают микросхемы статических ОЗУ с многоразрядной словарной организацией. Принцип построения таких микросхем рассмотрим.на примере микросхемы КР537РУ8, имеющей информационную емкость 2КХ8 бит (рис. 2.4). Она включает матрицу накопителя с 128X128 ЭП, регистры и дешифраторы кода адреса строк и столбцов, усилители записи- считывания, устройство управления и устройство ввода-вывода. Условное изображение микросхемы приведено на рис. 1.5,6. В качестве ЭП применен триггер на КМДП-транзйсторах (см. рис. 2.2).

Накопитель разбит на восемь секций по 128X16 ЭП в каждой. Четыре младших разряда кода адреса А0 — Аз выбирают по одному столбцу в каждой секции и коммутируют их с УВВ.

Управление устройством ввода-вывода осуществляют сигналы CS, Т)Е и W/R, предварительно обработанные устройством управления. В соответствии с табл. 1.3 в зависимости от значений управляющих сигналов микросхема может работать в одном из трех режимов: записи, считывания и хранения. В режиме записи информация 8-разрядным кодом через УВВ и усилители записи-считывания поступает в выбранную ячейку памяти. При считывании информация из выбранной ячейки памяти поступает на_УВВ и через него—на выходы. Сигнал разрешения выхода ОЕ позволяет в режиме считывания запрещать вывод информации: при ОЕ=1 входы-выходы принимают третье (высокоомное) состояние, так что информация на выходах отсутствует.

В режиме хранения потребляемая микросхемами от источника питания мощность снижается более чем в 1000 раз.

Номенклатура отечественных микросхем статических. ОЗУ достаточно представительна и разнообразна, чтобы удовлетворить широкий круг требований (табл. 2.1). Юна включает серии наиболее быстродействующих микросхем памяти, выполненных по технологиям ЭСЛ (К500, К1500), я-МДП ' (К132), ТТЛ (К155), с временем цикла обращения от 9 до 90 не, и серии КМДП-микросхем со сравнительно небольшим быстродействием 'и эп (сч) = 100 ... 800 не, но существенно меньшим уровнем потребляемой мощности: К537, К581, К561, К176. Эта особенность КМДП-микросхем обусловливает их перспективность для применения в устройствах с существенно ограниченным энергоресурсом, а также для построения энергонезависимых ОЗУ

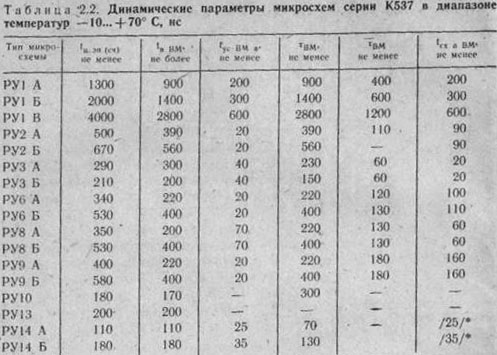

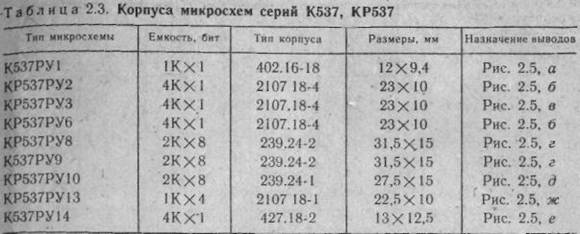

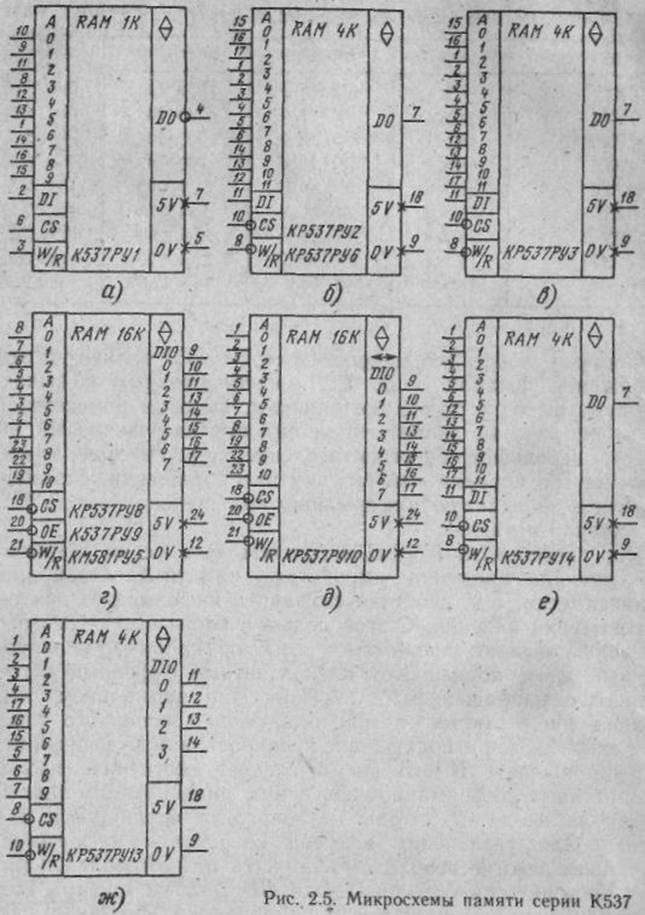

Наиболее развитым функциональным составом из серий КМДП-микросхем обладает серия К537. Место этой серии среди других по отдельным характеристикам видно из табл. 2.1. Более подробные сведения о ней приведены в табл. 2.2. Функциональный ряд серии включает более 15 типов микросхем, отличающихся информационной емкостью (от 1024 до 16 384 бит), организацией (одноразрядная и байтовая), быстродействием (более чем в 5 раз), уровнем потребляемой мощности. Имеются отличия и в системе управляющих сигналов и в конструктивном, оформлении (табл. 2.3). Назначение выводов корпусов микросхем серии К537 указано на рис. 2.5.

Общими свойствами микросхем серии К537 являются: единое напряжение питания 5 В, ТТЛ-уровни входных и выходных сигналов, выход с тремя состояниями, высокая помехоустойчивость, допустимая значительная емкость нагрузки (200 пФ и более), небольшое энергопотребление, причем при хранении почти на три порядка меньше, чем при обращении, способность сохранять записанную информацию при пониженном до 2...3 В напряжении питания.

Эту способность КМДП-микросхем всех серий широко используют для придания устройствам памяти свойства энергонезависимости, т. е'. свойства сохранять информацию при сбоях и отключении питания. С этой целью в блоке статического ОЗУ к выводам питания микросхем через ключ, например полупроводниковый диод, подключают низковольтный буферный источник питания с напряжением 2 ... 3 В. При нормальном режиме питания диод закрыт, а при выключении основного питания диод открывается и подключает к,микросхемам буферный источник напряжения. В это время.' следует обеспечить изоляцию накопителя по информационным цепям запрещающим значением уровня на входе CS, чтобы не повредить хранящуюся информацию. Для увеличения времени сохранения информации в аварийном режиме необходимо снижать ток потребления микросхем, повышать емкость низковольтных малогабаритных элементов питания и уменьшать,ток их саморазряда. Например, расчетное время сохранения информации микросхемой КР537РУЗА при работе от гальванического элемента СЦ-32 (1,57 В, 110 мА-ч) с учетом саморазряда элемента составляет тысячи часов. Некоторые микросхемы статических ОЗУ зарубежного производства снабжены встроенными в корпус гальваническими элементами, как, например, микросхема MK48Z02 (информационная емкость 2КХ8 бит) с двумя литиевыми элементами. В этой микросхеме на одном с ОЗУ полупроводниковом кристалле изготовлены устройство индикации уровня напряжения питания и устройство

переключения питания на резервное. Расчетное время сохранения информации в аварийном режиме составляет десятки лет. Известны разработки таких же микросхем памяти с емкостью 8К и 32К байт [20].

В устройствах памяти на микросхемах серии К537 для снижения потребляемой мощности следует предусмотреть возмож^ ность автоматического переключения питания микросхем в режиме хранения с основного источника 5 В на маломощный буферный источник напряжения, который обеспечивает питание только микросхем ОЗУ на уровне, достаточном для сохранения информации. Для микросхем К537РУ1, К.Р537РУ8 допускается снижать напряжение до 3 В, для микросхем КР537РУ6, К537РУ9 —до 3,3 В, для микросхем ' КР537РУ4, КР537РУ13, К537РУ14 — до 2,2 В. Наименьшую мощность от низковольтного источника питания потребляют микросхемы КР537РУЗА (ПмкВт), КР537РУ6А (115 мкВт), К537РУ13 и К537РУ14 (ЮОмкВт).

Микросхемы на МДП-транзисторах любого типа чувствительны к воздействию статического электричества из-за высокого входного сопротивления. Даже кратковременное повышение входного напряжения с недопустимо высоким уровнем может вызвать электрический пробой тонкого слоя подзатворного диэлектрика. Для защиты от вредного воздействия перенапряжения все входы микросхем защищают диодно-резистивными цепями, встроенными внутрь кристалла (см. рис. 2.3, б). Защитные цепи построены по схеме последовательного соединения двух диодов VD1, VD2 и токоограничивающего резистора R. От воздействия высокого положительного потенциала на входе защищает диод VD1, который при открывании фиксирует'входное напряжение на уровне напряжения питания. Высокий отрицательный потенциал открывает диод VD2, который ограничивает его безопасным ,для микросхемы уровнем.

Для -многих типов КМДП-микросхем,. и в частности для •микросхем серии К537, существует опасность теплового пробоя р-п переходов в кристалле из-за «тиристорного эффекта».

Сущность этого явления заключается в том, что при повышении напряжения в шине питания до 11 ... 12 В из-за бросков тока, при включении и влияния индуктивностей шин-, а также при превышении входным сигналом напряжения питания внутри кристалла активизируются .паразитные биполярные р-п-р-п структуры и из-за наличия положительной обратной связи по. цепям токов утечки может появиться эффект неуправляемого нарастания тока стока, близкий по механизму к аналогичному явлению в тиристорах в момент их переключения. Поскольку в КМДП-структурах отсутствуют токоогранйчивающие резисторы нагрузки, то нарастание тока приводит к развитию теплового пробоя в кристалле и, как следствие, к неисправности микросхемы.

С повышением уровня интеграции микросхем опасность возникновения в них тиристорного эффекта увеличивается. В некоторых типах микросхем рассмотренный эффект практически не наблюдается, в частности в микросхемах серий К561-, 564, в некоторых микросхемах серий К.537, например КР537РУ6 и др! В структурах этих микросхем сформированы так называемые «охранные кольца», шунтирующие паразитные транзисторы и за

счет этого устраняющие тиристорный эффект. Для тех микросхем, у которых защита отсутствует, необходимо предусматривать конструктивные меры предупреждения тиристорного эффекта: снижать индуктивность шин питания, не допускать близкого расположения с сильноточными микросхемами и т.д. [16].

При применении микросхем памяти, изготовленных по КМДП-технологии, в частности микросхем серии К537, необходимо соблюдать порядок включения питания и подачи входных сигналов: вначале должно быть включено напряжение питания. При выключении блока ОЗУ следует снять входные сигналы (адресные, управляющие и информационные) и затем отключить источник напряжения питания. Необходимо обеспечить также выполнение условия, по которому напряжение сигналов не Должно превышать напряжения питания микросхемы.

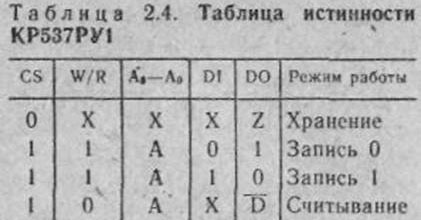

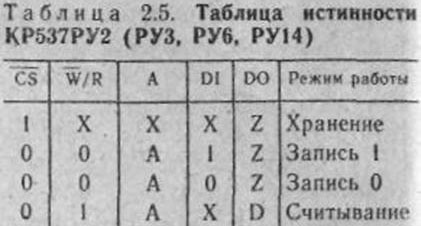

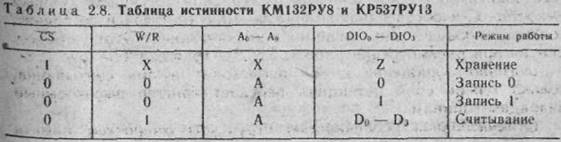

Микросхемы серии К537 работают в режимах записи, считывания и хранения. Значения сигналов в названных режимах указаны в табл. 2.4 для микросхемы К537РУ1, в табл. 2.5 для микросхем КР537.РУ2, КР537РУЗ, КР537РУ6, К537РУ14, в табл. 1.3 для микросхем КР537РУ8, К537РУ9, КР537РУ10 и в табл. 2.8 для микросхемы КР537РУ13.

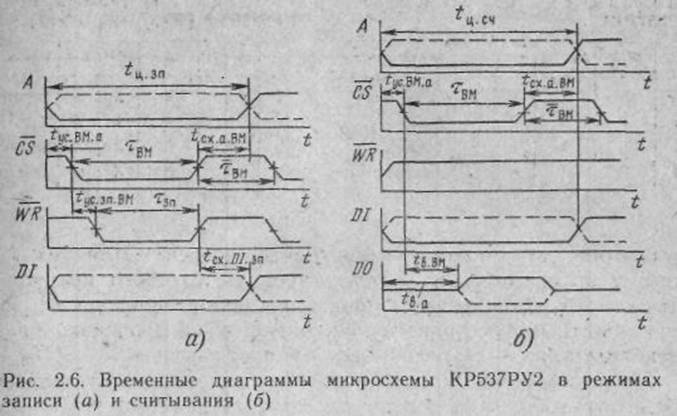

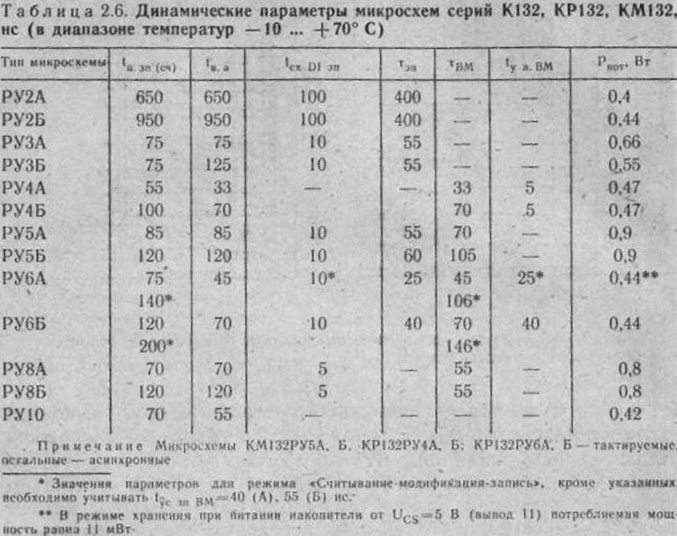

Сравнение динамических параметров микросхем, представленных в табл. 2.2, показыв'ает, что в серии К537 наибольшим быстродействием обладают микросхемы КР537РУ10 и К.537РУ14. Микросхемы К537РУ14 и КР537РУ13 являются асинхронными. За этим .исключением все микросхемы серии К537 являются тактируемыми: в режимах записи и считывания необходимо сигнал CS подавать импульсом, а сигнал W/R может иметь форму уровня напряжения или импульса, как показано на временных Диаграммах на рис. 2.6.

В режиме считывания информация на выходе появляется спустя время tB вм после отрицательного перепада сигнала CS (рис. 2.6, б). Время выборки адреса будет состоять из tB BM и tyc вм а. значения которых приведены в табл. 2.2.

Микросхемы КР537РУ8 и КР537РУ10. имеют дополнительный управляющий сигнал ОЕ (Разрешение 'по выходу): при подаче этого сигнала одновременно с сигналом CS отсчет времени появления сигнала ведется от отрицательного перепада сигнала

CS = OE. Существует возможность стробирования выходной

информации сигналом ОЕ, подаваемым с некоторой задержкой 'относительно сигнала CS. В этом случае при ОЕ = 1, т.е. до момента подачи этого сигнала, выходы находятся в третьем состоянии даже при CS=^0 (см. табл. 1.3). Только в момент поступления сигнала ОЕ выходы переходят в функциональное состояние: спустя время tB 0Е невыходах появится считываемая информация. В этом режиме время выборки адреса определяют соотношениями: tB a=tyc ОЕ.а + te.OE Либо tв „ = tус вм а + tyc 0Е вм +

<-f-tB ое- Заметим, что tyc0E.BM не регламентируют, его значение устанавливают, исходя из условий работы микросхемы в составе устройства.

Микросхема КМ581РУ5 Б, В, Г также выполнена по КМДП-технологии. Она представляет собой статическое асинхронное ОЗУ емкостью 2КХ8 бит. Конструктивно оформлена в корпусе 2120.24-11, назначение выводов идентично микросхемам КР537РУ8 и К537РУ9 (рис. 2.5, г). Таблица истинности соответствует табл. 1.3. Электрические характеристики микросхемы приведены в табл. 2.1. Следует добавить, что микросхема дифференцирована по группам Б, В, Г по значению временных пара-

г метров: время цикла записи (считывания) составляет 120 не (Б), 150 не (В), 200 не (Г), т.е. микросхемы группы Б обладают наибольшим быстродействием. Выходной ток 4 мД. Выход построен по схеме с тремя состояниями.

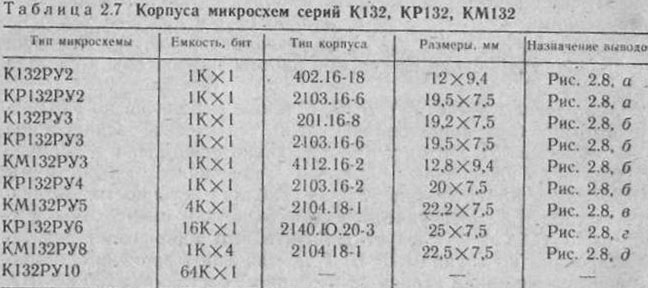

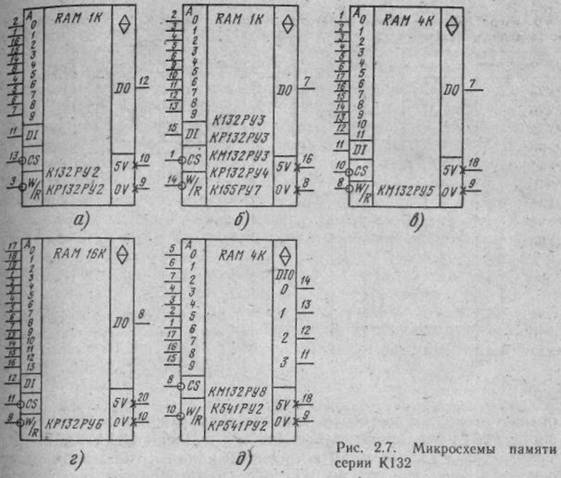

Серия К132 состоит из микросхем статических ОЗУ высокого быстродействия: время цикла обращения для большинства микросхем лежит в диапазоне значений 55 ... 85 не (табл. 2.1). Мик-

. росхемы выполнены по «-канальной МДП-технолбгий и отличаются разнообразием в отношении структурных и схемотехнйче-

ских решений, электрических параметров (табл. 2.6), конструкций корпуса (табл. 2.7, рис. 2.7).

Однако у микросхем серии К132 имеются ряд общих свойств, важных для их практического использования: единое напряжение питания 5 В, ТТЛ входные и выходные уровни напряжений О и !: входные—соответственно не более 0,8 В, не менее 2 В, выходные — не более 0,4 В, не менее 2,4 В; наличие выходов с тремя состояниями, единая система сигналов управления: CS, W/R; способность работать на большую емкостную нагрузку (от 100 до 600 пФ для разных типов микросхем), возможность снижения уровня энергопотребления при переходе в режим хранения в 3—5 раз, а у некоторых микросхем —до 20 раз

.

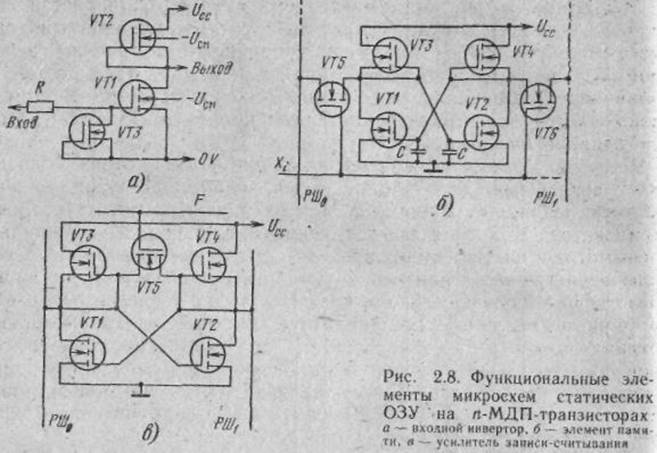

По своей структуре микросхемы серии К132 близки к микросхемам рассмотренных серий К561, К.537: они состоят из накопителя матричного типа, регистров и дешифраторов кода адреса, устройства ввода-вывода, блока ключей выбора строк и столбцов. В реализации названных элементов структурной схемы также имеется много общих решений. В частности, все входы — адресные, управляющие, информационные, имеют .усилители, построенные по схеме (рис. 2.8, а) инвертора на двух транзисторах VT1, VT2 с защитой в виде резистивно-транзисторной цепи R, VT3. Охранный транзистор VT3 своим р-п переходом сток-Цодложка предохраняет вход транзистора VT1 от действия статического электричества и защищает от резких бросков напряжений на входах своей выходной емкостью, которая вместе с резистором образует интегрирующую цепочку.

Входные усилители-формирователи обладают высоким быст-

родействием, которое обеспечено выбором режима работы' транзистора VT2 и напряжением смещения подложки Uc„=— 2,7 В. Транзистор VT2, имеющий встроенный канал я-типа, нормально открыт и при выключении VT1 переходит в .режим генератора тока, заряжая за короткое время выходную емкость. При включении VT1 емкость также быстро разряжается через низкоомный канал открытого транзистора VT1.

Напряжение отрицательного смещения р-подложки формирует встроенный в кристалл преобразователь из напряжения питания микросхемы 5 В. Это напряжение уменьшает порог включения транзисторов и снижает .уровень токов утечки внутри кристалла.

В качестве ЭП применяют статический триггер (рис. 2.8, б)

на четырех транзисторах. VT1 — VT4 и двух ключевых транзи

сторах VT5, VT6, затворы которых соединены с адресной шиной,

а стоки — с разрядными шинами. При Х, = 1 ключевые транзи

сторы открываются и подключают триггер к разрядным шинам.

При записи разрядные шины передают свой потенциал узловым

емкостям С и обеспечивают переключение триггера в состояние,

соответствующее записываемой информации. Этот процесс

описан при рассмотрении работы КМДП-триггера (см. рис. 2.2)

Аналогично' обращение к ЭП происходит и при считывании,

только теперь свой потенциал передает триггер высокоомным

разрядным шинам. '; ,,

Отличительной особенностью структуры микросхем памяти

д-МДП-типа, в частности микросхем серии К132, является наличие в каждом столбце усилителя записи-считывания триггер-ного типа (рис. 2i8, в). Усилитель управляется внутренним сигналом F: при его поступлении транзистор VT5 открывается и уравнивает потенциалы двух входов-выходов триггера. В этом и заключается подготовка усилителя к приему информации. При считывании информации с выбранного ЭП на разрядных шинах •рШо, РШ| создается асимметрия потенциалов, которая оказывает воздействие на состояние плеч усилителя, подключенного к этим разрядным шинам. В момент снятия сигнала F, когда транзистор VT5 закрывается, вносимая разрядными шинами асимметрия потенциалов определит состояние, в которое переключится триггер-усилитель. В результате слабый информационный сигнал, полученный с выхода ЭП, будет усилен и передан в устройство ввода-вывода. Усилитель составлен из транзисторов, отличающихся от транзисторов ЭП более высоким уровнем токов. Одновременно с усилением считываемого сигнала триггер-усилитель предотвращает возможность разрушения информации в выбранном ЭП, так как обеспечивает восстановление (регенерацию) заряда узловых емкостей триггера ЭП.

В некоторых микросхемах, например в КР132РУ6, К.132РУ10 и др., ЭП выполнен на триггере, в котором вместо нагрузочных транзисторов сформированы высокоомные (до 109 Ом) резисторы. При такой технологии удается обеспечить более высокий уровень интеграции и, следовательно, увеличение информационной емкости микросхемы памяти. Кроме того, снижается потребляемая микросхемой мощность в режиме хранения.

Применение высокОомных резисторов в схеме триггера оказалось возможным благодаря усовершенствованию «-канальной технологии и снижению на этой основе паразитных токов утечки в структуре кристалла до значений Тшкоампер [19]. Выходные каскады микросхем построены по схеме инверторов с тремя состояниями, формирующими ТТЛ-уровни.

Микросхемы серии К132 работают в режимах записи, считы-. вания и хранения. Таблицы истинности всех микросхем серии К132, кроме К.М132РУ8, соответствуют содержанию табл. 2.5. Таблица истинности микросхемы К.М132РУ8 (табл. 2.8) имеет отличия, обусловленные тем, что у этой микросхемы входы и вы-

ходы совмещены. Микросхема КР132РУ6 имеет дополнительно к названным режим «Считывание-модификация-запись». Отличительные особенности этого режима проявляются в динамике работы микросхемы и видны на временных диаграммах. Эти особенности будут рассмотрены ниже.

При реализации названных режимов следует учитывать тре

бования к форме представления сигналов управления: сигнала

разрешения выбора микросхемы CS и сигнала режима обраще

ния W/R. По этому признаку, как уже отмечалось в § 1.2, микро

схемы статических ОЗУ делят на асинхронные и тактируемые.

Микросхемы КР132РУ4А, Б, КМ132РУ5А, Б и КР132РУ6А, Б

являются тактируемыми (КМ132РУ5А, Б — только в режиме

записи), остальные микросхемы этой серии — асинхронные.

Временные диаграммы для тактируемых микросхем аналогичны

диаграммам на рис; 2.6. Напомним, что при записи и считывании

информации у тактируемых микросхем сигнал CS или W/R

подается импульсом. При схемотехнической реализации вре

менных диаграмм сигналов микросхемы необходимо руководст

воваться значениями временных параметров, основные из ко

торых приведены в табл. 2.6. У микросхем КР132РУ4 и КР132РУ6

адресные, управляющие и информационные сигналы фиксируют

ся («защелкиваются») на входных усилителях-триггерах по от

рицательному'перепаду сигнала CS. Поэтому для этих микросхем

необходимб обеспечить требуемое время удержания названных

сигналов относительно сигнала CS для их «захвата» входными

триггерами. После фиксации сигналы могут принимать произ

вольные значения, например значения для следующего цикла

обращения. У микросхем асинхронных ОЗУ сигналы CS и W/R. можно подавать уровнем 0 или 1. В таком случае временные процессы в микросхеме определяют адресные сигналы. В асинхронных микросхемах управляющие сигналы можно подавать и импульсами. Тогда надо принимать во внимание требования к их минимальной длительности (табл. 2.6).

Режим «Считывание-модификация-запись» совмещает в себе два режима и обеспечивает считывание информации из выбранного ЭП и запись в этот же ЭП новой информации в одном цикле (рис. 2.9). Время цикла обращения к микросхеме в том режиме больше (см. табл. 2.6 для КР132РУ6). Увеличивается и число учитываемых временных параметров.

Для обеспечения максимального быстродействия микросхем необходимо адресные сигналы и сигналы управления формировать с длительностью фронта 2 не.

В режиме хранения у многих микросхем серии К132 наблюдается снижение в 3—5 раз тока потребления. У микросхем К132РУ6 и К.М132РУ8 возможно многократное (более чем в 10 раз) снижение потребляемой мощности за счет выключения напряжения питания, но сохранения его уровня 5 В на выводе CS. В этом режиме через вход CS осуществляется питание только накопителя и формирователя напряжения смещения подложки, остальные функциональные узлы микросхемы находятся в выключенном состоянии.

Большая интегральная схема К1809РУ1 представляет собой статическое ОЗУ емкостью 1К.Х16 бит. Особенность микросхемы состоит в том, что она имеет встроенный интерфейс, т. е. функциональные узлы, которые обеспечивают режим обмена со стан- • дартной магистралью микроЭВМ «Электроника-60». Благодаря наличию встроенного интерфейса микросхему можно непосредственно подключать к магистрали [21].

Структурная схема включает накопитель, дешифраторы адреса строк и столбцов, схему управления (контроллер), обеспечивающую ввод и вывод кода адреса, данных, сигналов управления. Кроме того, в» структуру включен блок задания адреса микросхемы, который представляет собой программируемое устройство для дешифрирования 5-разрядного кода выбора микросхемы. Этот блок состоит из регистра и схемы сравнения. Предварительно в регистр заносится адрес микросхемы. При работе в блоке происходит сравнение принятого кода адреса с записанным в регистр, и при совпадении на выходе вырабатывается сигнал разрешения записи данных в микросхему. В случае несовпадения данные, пришедшие с «чужим» адресом, записаны быть не могут. Наличие встроенного блока задания адреса позволяет формировать модуль ОЗУ из 32 микросхем без внешнего устройства выбора микросхемы.

Более подробно устройство и возможности этой БИС из

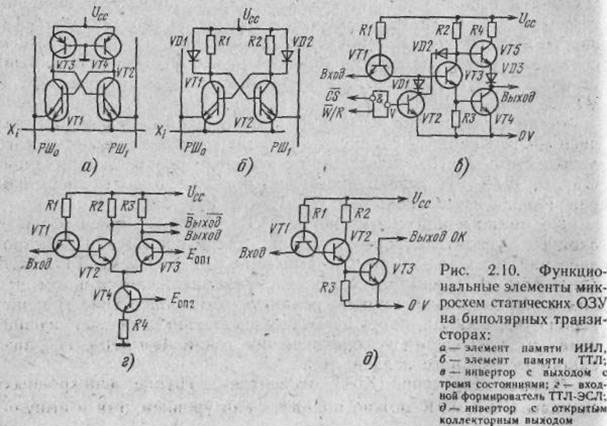

ложены в § З.1.: Серии К155, К134, К.541, К185, К500, КJ500 и др. содержат микросхемы, изготовленные методами биполярной технологии-Среди этих методов наиболее широко применяются методы ТТЛ-' технологии, сейчас в основном ТТЛШ (серии К531, К1531, К1533 и др.), ЭСЛ-технологии (серии К500, K15U0), технологии ИИЛ в сочетании с ТТЛ (К185, К134, К541 и др.), ТТЛ с ЭСЛ (К155) и т. д. Названные технологии отличаются схемотехническими решениями, принятыми для микросхем статических- ОЗУ. Объединяет эти технологии то, что основным активным компонентом схем является биполярный транзистор и, следовательно, в основе лежит технология изготовления биполярных структур с различными физико-техническими свойствами: классических п-р-п или р-п-р транзисторов, транзисторов с включением диодов Шот-ки параллельно коллекторному переходу (транзисторов Шотки), тиристоров, транзисторов с инжекционным питанием и т. д.

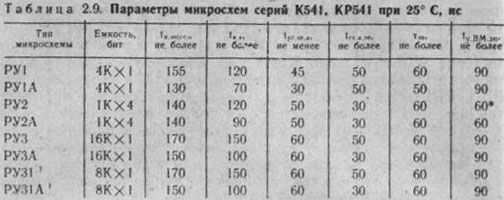

Серия К541 имеет в своем составе микросхемы статических ОЗУ емкостью 4КХ1, 8КХ1, 16КХ1, 1КХ4 асинхронного типа среднего быстродействия (табл. 2.1). Микросхемы серии имеют напряжение питания 5 В, ТТЛ входные и выходные уровни, выход на три состояния, характеризуются сравнительно высоким уровнем энергопотребления, по сравнению с микросхемами серии К132, причем не обладают свойством снижать уровень потребляемой мощности в режиме хранения.

Структура микросхем содержит все функциональные узлы типичного варианта ее построения (рис. z.l(J). В качестве элемента памяти использован статический триггер на четырех транзисторах, два из которых, VT3 и VT4, являются инжекторами транзисторов VT2 и VTI соответственно. Двухэмиттерными транзисторами управляют сигналы адресной шины X; и разрядных шин РШо, РШ*. При X, =0 триггер находится в режиме хранения, так как при этом фиксируется состояние плеч триггера. При Х, = 1 оба эмиттерных перехода, подключенных к адресной шине, закрываются и состояние триггера зависит от потенциалов разрядных шин: при низком потенциале шин в режиме считывания в одну из них потечет ток, а именно в ту, со стороны которой транзистор открыт; в другой тока не будет.

. При_записи по шинам в форме парафазного сигнала РШ( = D, РШо = 0 к плечам триггера подводится информация. Асимметрия в потенциалах шин вызовет переключение' триггера в состояние, определяемое потенциалами шин: например, при РШ|=0; РШо=1 (запись 0) откроется VT2, через него в шину потечет ток инжектора VT4, а транзистор VT1 закроется. При записи 1 состояния транзисторов изменятся на обратные.

Выходные и входные цепи выполнены на элементах ТТЛ, поскольку низкопороговые функциональные узлы ИИЛ имеют низкую помехоустойчивость и, кроме того, не согласованы по уровням напряжения с элементами других типов логики. Вариант выходного каскада с тремя состояниями (рис. 2.10, в) выполнен по схеме ТТЛ сложного инвертора с дополнительными элементами VD1, VD2, VT2, необходимыми для обеспечения третьего состояния выхода. Управляющий сигнал V зависит от внешних сигналов CS и W/R, воздействуя на вход транзистора' VT2, закрывает его при V=0 или открывает при V=K В третьем состоянии выход находится при V=l, когда открытый транзистор VT2 шунтирует входы и. закрывает транзисторы VT5 и. VT3, а значит, и VT4. -

Микросхемы серии К541 работают в режимах хранения, записи и считывания. Условия реализации этих режимов представлены в табл. 2.5. В соответствии с условием режима считывания: "US = 0,W/R=1, "управляющий сигнал должен быть сформирован, исходя из соотношения: V = CS-W/R или CS + W/R.

По аналогичной схеме, но без VD1, VD2, VT2 построены и входные усилители-формирователи. Для повышения быстродействия входные усилители выполняют и по схеме ТТЛ-ЭСЛ (рис. 2,10, г). Преимущество этой схемы заключается в том, что она в максимальной степени реализует быстродействие транзисторов, что, вбобще, присуще ЭСЛ-схемотехнике, за счет ограничения их насыщения и переключения током эмиттера, не зависящим от входного воздействия.

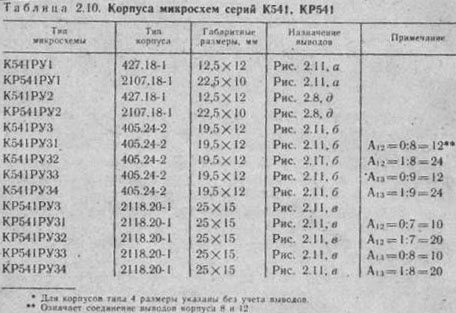

Микросхемы серии К541 относятся к группе асинхронных: сигналы~С1Г иЛУ/R можно подавать как уровнем, так и импульсом. Параметры микросхем представлены в табл. 2.9, а данные о конструктивном оформлении — в табл. 2.10 и на рис. 2.11.

Микросхемы ОЗУ серий К134, К155, К185 имеют много общего с рассмотренными. Все они относятся к.типу асинхронных статических ОЗУ^ поэтому достаточно просты в применении. Основные характеристики этих микросхем приведены в табл. 2.1. Обратим внимание лишь на некоторые особенности, знание которых необходимо для практики.

Микросхема К155РУ7 емкостью 1К X 1 бит, асинхронная, обладает повышенным быстродействием: ее время цикла обращения равно 45 не. Это достигнуто применением в структуре микросхемы элементов ТТЛ и ЭСЛ, в частности, элементом памяти является статический триггер на двухэмиттерных транзисторах (рис. 2.10, б) с нелинейной нагрузкой, а входные и выходные каскады выполнены по совмещенной схемотехнике, как показано на рис. 2.10, г. Таблица истинности, динамика работы этой микросхемы аналогичны микросхемам серии К541. Конструктивное выполнение— пластмассовый корпус 238.16-2, назначение выводов по рис. 2.8, б.

Микросхема К134РУ6 емкостью 1КХ 1 бит получена по ИИЛ-ТТЛ-технологии. Ее особенность заключается в том, что выход построен по схеме с открытым коллектором ОК (рис. 2.10, д). Наличие такого выхода не позволяет объединять информационные входы и выходы. При соединении нескольких микросхем по выходам можно использовать схему «монтажного ИЛИ» с подключением к точке соединения источника питания через внешний токоограничивающий резистор. Для расчета его сопротивления необходимо учитывать прежде всего значение выходного тока в состоянии логического 0, равное 16 мА. Характеристики микросхем приведены в табл. 2.1. При хранении потребляемая мощность снижается вдвое.

У микросхемы К185РУ5 емкостью 1КХ1 бит те же особенности, что и у К134РУ6, но она более быстродействующая. В динамике работы при обращении в момент воздействия сигнала CS на выходе возможны помехи длительностью не более чем время выбора: tBg,\i- Серия развивается, о чем свидетельствуют микросхемы К185РУ10 емкостью 16К.Х1 бит с временем цикла 50 не.

Микросхемы серий К500, К1500 обладают самым большим быстродействием, что обусловлено использованием для их изготовления ЭСЛ-технологии. Микросхемы относятся к группе асинхронных.

Время цикла обращения в диапазоне рабочих тем ператур имеет значения от 9 не для микросхемы К1500РУ073 и 15 не для К1500РУ480 до 40... 45 не для К500РУ470, К1500РУ470, К500РУ415. Микросхемы памяти названных серий имеют электрические характеристики, несовместимые с характеристиками микросхем других серий, что исключает их совместное применение. Для них характерен сравнительно высокий уровень энергопотребления при небольшой информационной емкости (табл. 2.1). Причем уровень потребляемой мощности не изменяется при переходе от режима обращения к режиму хранения. Выход у большинства микросхем построен по схеме с открытым эмиттером (ОЭ). Такой выход можно непосредственно подключать к информационной шине либо необходимо его нагрузить внешним резистором 50 Ом, соединенным с источником напряжения.—2 В. Микросхемы памяти ЭСЛ-серий предназначены в основном для применения в быстродействующей аппаратуре в качестве регистров процессора (микросхемы с организацией 16X4, 64X8 и др.), сверхоперативной и буферной памяти (микросхемы с организацией 256X1, 256X4, 1КХ 1, 4КХ1, 1КХ4)

|