Памятью ЭВМ называется совокупность устройств, служащих для запоминания, хранения и выдачи информации. Отдельные устройства, входящие в эту совокупность, называют запоминающими устройствами или памятями того или иного типа.

Оба эти термина в настоящее время стали почти синонимами. Однако термин «запоминающее устройство» (ЗУ) обычно употребляют, когда речь идет о принципе построения некоторого устройства памяти (например, полупроводниковые ЗУ, ЗУ на магнитных дисках и т.д.), а термин «память» — когда хотят подчеркнуть выполняемую устройством памяти логическую функцию или место расположения в составе оборудования ЭВМ (например, оперативная память, внешняя память и т.д.).

Производительность и вычислительные возможности ЭВМ в значительной степени определяются составом и характеристиками ее ЗУ. В составе ЭВМ используется одновременно несколько типов ЗУ (несколько типов памятей), отличающихся принципом действия, характеристиками и назначением.

Продолжительность обращения (время цикла) при записи Основными операциями в памяти в общем случае являются занесение информации в память — запись и выборка информации из памяти — считывание. Обе эти операции называются

обращением к памяти, или, подробнее, обращением при считывании и обращением при записи: ****>«

При обращении к памяти производится считывание или запись некоторой единицы данных — различной для устройств разного типа. Такой единицей может быть, например, байт, машинное слово или блок данных.

Важнейшими характеристиками отдельных устройств памяти (запоминающих устройств) являются емкость памяти, удельная емкость, быстродействие.

Емкость памяти определяется максимальным количеством данных, которые могут в ней храниться. Емкость измеряется в двоичных единицах (битах), машинных словах, но большей частью в байтах (1 байт = 8 бит), при этом часто емкость памяти выражают через число К=Ю24: Кбит (килобит), Кслов (килослов) или Кбайт (килобайт), при этом 1024 Кбайт обозначают как 1 Мбайт (мегабайт).

Удельная емкость есть отношение емкости ЗУ к его физическому объему.

Быстродействие памяти определяется продолжительностью операции обращения, т. е. временем, затрачиваемым на поиск нужной единицы информации в памяти и на ее считывание (время обращения при считывании), или временем на поиск места в памяти, предназначаемого для хранения данной единицы информации, и на ее запись в память (время обращения при записи).

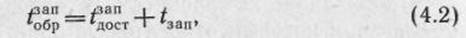

Продолжительность обращения к памяти (время цикла памяти) при считывании

где f™^ — время доступа, определяющееся промежутком времени между моментом начала операции обращения при считывании до момента, когда становится возможным доступ к данной единице информации; tC4m— продолжительность самого физического процесса считывания, т. е. процесса обнаружения и фиксации состояний соответствующих запоминающих элементов или участков поверхности носителя информации.

В некоторых устройствах памяти считывание информации сопровождается ее разрушением (стиранием). В таком случае цикл обращения должен содержать операцию восстановления (регенерации) считанной информации на прежнем месте в памяти.

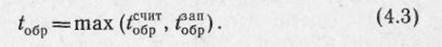

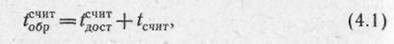

В качестве продолжительности цикла обращения к памяти принимается величина

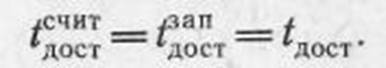

где *до"т — время доступа при записи, т. е. время от момента начала обращения при записи до момента, когда становится возможным доступ к запоминающим элементам (или участкам поверхности носителя), в которые производится запись; *подг — время подготовки, расходуемое на приведение в исходное состояние запоминающих элементов или участков поверхности носителя информации для записи определенной единицы информации (например, байта или слова); t3an— время занесения информации, т. е. изменения состояния запоминающих элементов (участков поверхности носителя). Большей частью

В зависимости от реализуемых в памяти операций обращения различают: а) память с произвольным обращением (возможны считывание и запись данных в память); б) память только для считывания информации («постоянная» или «односторонняя»). Запись информации в постоянную память производится в процессе ее изготовления или настройки1.

По способу организации доступа различают устройства памяти с непосредственным (произвольным), с прямым (циклическим) и последовательным доступами.

В памяти с непосредственным (произвольным) доступом время доступа, а поэтому и цикл обращения не зависят от места расположения участка памяти, с которого производится считывание или в который записывается информация. В большинстве случаев непосредственный доступ реализуется при помощи электронных (полупроводниковых) ЗУ. В подобных памятях цикл обращения обычно составляет 1 мкс или всего несколько сотен или десятков наносекунд. Число разрядов, считываемых или записываемых в памяти с непосредственным доступом параллельно во времени за одну операцию обращения, называется В двух других типах памяти используются более медленные электромеханические процессы. В устройствах памяти с прямым доступом, к которым относятся устройства с магнитными барабанами и дисками, благодаря непрерывному вращению носителя информации возможность обращения к некоторому участку носителя для считывания или записи циклически повторяется. В такой памяти время доступа составляет обычно от нескольких долей секунды до нескольких десятков миллисекунд.

В памяти с последовательным доступом производится последовательный просмотр участков носителя информации, пока нужный участок носителя не займет некоторое исходное положение. Характерным примером является ЗУ на магнитных лентах. Время доступа может в неблагоприятных случаях расположения информации достигнуть нескольких минут.

Запоминающие устройства различаются также по выполняемым в ЭВМ функциям, зависящим в частности, от места расположения ЗУ в структуре ЭВМ.

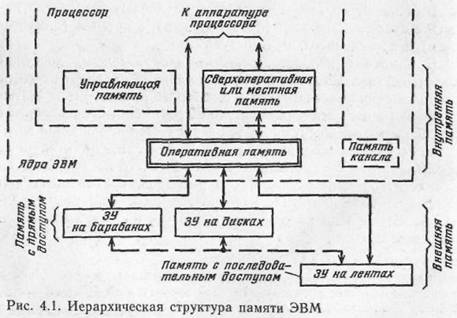

Требования к емкости и быстродействию памяти являются противоречивыми. Чем больше быстродействие, тем технически труднее достигается и дороже обходится увеличение емкости памяти. Стоимость памяти составляет значительную часть общей стоимости ЭВМ. Поэтому память ЭВМ организуется в виде иерархической структуры запоминающих устройств, обладающих различными быстродействием и емкостью (рис. 4.1). В общем случае ЭВМ содержит сверхоперативную память (СОП)

или местную память, оперативную или основную память (ОП), память с прямым доступом на магнитных барабанах и на магнитных дисках, память с последовательным доступом на магнитных лентах. Порядок перечисления устройств соответствует убыванию их быстродействия и возрастанию емкости. Каждый уровень иерархии может содержать несколько экземпляров (модулей) соответствующих устройств для получения нужной емкости данного уровня памяти. На рис. 4.1 сплошными и штриховыми линиями показаны соответственно обычно и сравнительно редко реализуемые пути передачи данных между отдельными ступенями иерархической памяти. Иерархическая структура памяти позволяет экономически эффективно сочетать хранение больших объемов информации с быстрым доступом к информации в процессе обработки.

Оперативной или основной памятью (ОП) называют устройство, которое служит для хранения информации (данных программ, промежуточных и конечных результатов обработки), непосредственно используемой в процессе выполнения операций в арифметическо-логическом устройстве и устройстве управления процессора.

В процессе обработки информации осуществляется тесное взаимодействие процессора и ОП. Из ОП в процессор поступают команды программы и операнды, над которыми производятся предусмотренные командой операции, а из процессора в ОП направляются для хранения промежуточные и конечные результаты обработки.

Характеристики ОП непосредственно влияют на основные показатели ЭВМ и в первую очередь на скорость ее работы. Оперативная память высокопроизводительных ЭВМ имеет емкость несколько миллионов байт и цикл обращения около 0,5 мкс (и менее). Запоминающие устройства ОП, ранее выполнявшиеся на магнитных (ферритовых) сердечниках и тонких магнитных пленках, в настоящее время изготовляются на интегральных микросхемах с большой степенью интеграции (полупроводниковые ЗУ).

В ряде случаев быстродействие ОП оказывается недостаточным, и в состав машины приходится включать СОП (буферную или кэш-память на несколько сотен или тысяч машинных слов с циклом обращения, составляющим несколько десятков наносекунд. Такие СОП выполняются на быстродействующих интегральных микросхемах. Быстродействие СОП должно соответствовать скорости работы арифметическо-логических и управляющих устройств процессора. Сверхоперативная (буферная) память используется для промежуточного хранения считываемых процессором из ОП участков программы и групп данных, в качестве рабочих ячеек программы, индексных регистров, для хранения служебной информации, используемой при управлении вычислительным процессом. Она выполняет роль согласующего звена между быстродействующими логическими устройствами процессора и более медленной ОП (см. гл. 14).

В качестве ОП и СОП используются быстродействующие ЗУ с произвольным обращением и непосредственным доступом.

Понятие оперативной памяти выше определялось, исходя из выполняемых ею функций. Поскольку всегда в качестве ОП (как, впрочем, и СОП) используются ЗУ с произвольным обращением и непосредственным доступом, то часто последние независимо от выполняемых функций называют оперативными памятями (оперативными ЗУ).

Обычно емкость ОП оказывается недостаточной для хранения всех необходимых данных в ЭВМ. Поэтому ЭВМ содержит в своем составе несколько ЗУ с прямым доступом на дисках (емкость одного ЗУ на дисках 10 — 300 Мбайт) и несколько ЗУ с последовательным доступом на магнитных лентах (емкость одного ЗУ 20—200 Мбайт).

Оперативная память вместе с СОП и некоторыми другими специализированными памятями процессора образуют внутреннюю память ЭВМ (рис. 4.1). Электромеханические ЗУ образуют внешнюю память ЭВМ, а сами они поэтому называются внешними запоминающими устройствами (ВЗУ).

Современные ЭВМ содержат ряд специализированных быстродействующих памятей: памяти каналов, ключей защиты памяти, отдельных типов терминалов (дисплеев и др.), различные буферные памяти для промежуточного хранения информации при обмене ею между устройствами машины, работающими с различными скоростями. Наряду с этим используются также постоянные памяти, в основном для хранения микропрограмм, а в специализированных ЭВМ — и для хранения основных программ.

Запоминающее устройство любого типа состоит из запоминающего массива, хранящего информацию, и блоков, служащих для поиска в массиве, записи и считывания (а в ряде случаев и для регенерации) информации.

Адресная, ассоциативная и стековая организации памяти

Запоминающее устройство с произвольным обращением, как правило, содержит множество одинаковых запоминающих элементов, образующих запоминающий массив (ЗМ). Массив разделен на отдельные ячейки; каждая из них предназначена для хранения двоичного кода, число разрядов в котором определяется шириной выборки памяти (в частности, это может быть одно, половина или несколько машинных слов). Способ организации памяти зависит от методов размещения и поиска информации в запоминающем массиве. По этому признаку различают адресную, ассоциативную и стековую (магазинную) памяти.

Адресная память. В памяти с адресной организацией размещение и поиск информации в ЗМ основаны на использовании адреса хранения слова (числа, команды и т. п.). Адресом служит номер ячейки ЗМ, в которой это слово размещается.

При записи (или считывании) слова в ЗМ инициирующая эту операцию команда должна указывать адрес (номер ячейки), по которому производится запись (считывание).

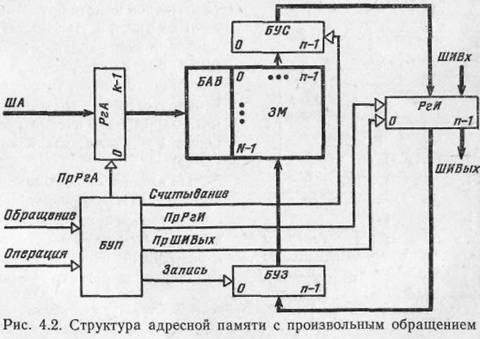

Типичная структура адресной памяти, показанная на рис. 4.2, содержит запоминающий массив из N «-разрядных ячеек и его аппаратурное обрамление, включающее в себя регистр адреса РгА, имеющий k(fe>logiV) разрядов, информационный регистр РгИ, блок адресной выборки БАВ, блок усилителей считывания БУС, блок разрядных усилителей-формирователей сигналов записи БУЗ и блок управления памятью БУП.

По коду адреса в РгА БАВ формирует в соответствующей ячейке памяти сигналы, позволяющие произвести в ячейке считывание или запись слова.

Цикл обращения к памяти инициируется поступлением в БУП извне сигнала Обращение. Общая часть цикла обращения включает в себя прием в РгА с шины адреса ША адреса

обращения и прием в БУП и расшифровку управляющего сигнала Операция, указывающего вид запрашиваемой операции (считывание или запись).

Далее при считывании БАВ дешифрирует адрес, посылает сигналы считывания в заданную адресом ячейку ЗМ, при этом код записанного в ячейке слова считывается усилителями считывания БУС и передается в РгИ. Операция считывания завершается выдачей слова из РгИ на выходную информационную шину ШИВых.

При записи помимо выполнения указанной выше общей части цикла обращения производится прием записываемого слова с входной информационной шины ШИВх и РгИ. Затем в выбранную БАВ ячейку записывается слово из РгИ.

Блок управления БУП генерирует необходимые последовательности управляющих сигналов, инициирующих работу отдельных узлов памяти. Цепи передачи управляющих сигналов показаны тонкими линиями на рис. 4.2.

Ассоциативная память. В памяти этого типа поиск нужной информации производится не по адресу, а по ее содержанию (по ассоциативному признаку). При этом поиск по ассоциативному признаку (или последовательно по отдельным разрядам этого признака) происходит параллельно во времени для всех ячеек запоминающего массива. Во многих случаях ассоциативный поиск позволяет существенно упростить и ускорить обработку данных. Это достигается за счет того, что в памяти этого типа операция считывания информации совмещена с выполнением

ряда логических операций. т

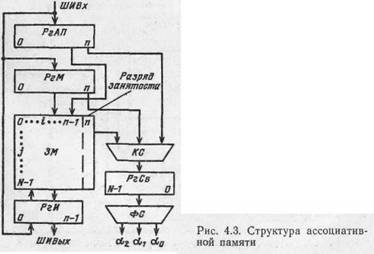

Типичная структура ассоциативной памяти представлена на рис. 4.3. Запоминающий массив содержит N разрядных ячеек. Для указания занятости ячейки используется служебный

tt-й разряд (0 — ячейка свободна, 1 — в ячейке записано слово).

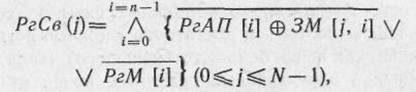

По входной информационной шине ШИВх в регистр ассоциативного признака РгАП в разряды 0 Ч-п— 1 поступает «-разрядный ассоциативный запрос, а в регистр маски РгМ — код маски поиска, при этом n-разряд ггм устанавливается в 0. Ассоциативный поиск производится лишь для совокупности разрядов РгАП, которым соответствуют 1 в РгМ (незамаскированные разряды РгАП). Для слов, в которых цифры в разрядах совпали с незамаскированными разрядами РгАП, комбинационная схема КС устанавливает 1 в соответствующие разряды регистра совпадения РгСв и 0 в остальные разряды. Таким образом, значение /-го разряда в РгСв определяется выражением

где РгАП [i], РгМ [г] и ЗМ [/, г] — значения г'-ro разряда соответственно РгАП, РгМ и ;'-й ячейки ЗМ.

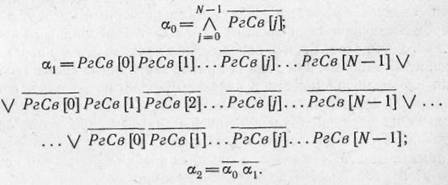

Комбинационная схема формирования результата ассоциативного обращения ФС формирует из слова, образовавшегося в РгСв, сигналы ссо, аь а2, соответствующие случаям отсутствия слов в ЗМ, удовлетворяющих ассоциативному признаку, и наличия одного (и более) такого слова. Для этого ФС реализует следующие булевы функции:

Формирование содержимого РгСв и сигналов ао, cti, аг по содержимому РгАП, РгМ и ЗМ называется операцией контроля ассоциации. Эта операция является составной частью операций считывания и записи, хотя она имеет и самостоятельное значение.

При считывании сначала производится контроль ассоциации по ассоциативному признаку в РгАП. Затем при а0=1 считывание отменяется из-за отсутствия искомой информации, при ос = = 1 считывается в РгИ найденное слово, при а2= 1 в РгИ считывается слово из ячейки, имеющей наименьший номер среди ячеек, отмеченных 1 у РгСв. Из РгИ считанное слово выдается на ШИВых.

При записи сначала отыскивается свободная ячейка. Для этого выполняется операция контроля ассоциации при РгАП — 111...10 и РгЛ4 = 00...01, при этом свободные ячейки отмечаются 1 в РгСв. Для записи выбирается свободная ячейка с наименьшим номером. В нее записывается слово, поступившее с ШИВх в РгИ.

С помощью операции контроля ассоциации можно, не считывая слов из памяти, определить по содержимому РгСв, сколько в памяти слов, удовлетворяющих ассоциативному признаку, например реализовать запросы типа сколько студентов в группе имеют отличную оценку по данной дисциплине. При использовании соответствующих комбинационных схем в ассоциативной памяти могут выполняться достаточно сложные логические операции, такие, как поиск большего (меньшего) числа, поиск слов, заключенных в определенных границах, поиск максимального (минимального) числа и др.

Отметим, что для ассоциативной памяти необходимы запоминающие элементы, допускающие считывание без разрушения записанной в них информации. Это связано с тем, что при ассоциативном поиске считывание производится по всему ЗМ для всех незамаскированных разрядов и негде сохранять временно разрушаемую считыванием информацию.

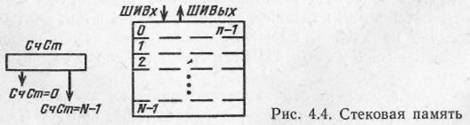

Стековая память, так же как и ассоциативная, является безадресной. Стековую память (рис. 4.4) можно рассматривать как совокупность ячеек, образующих одномерный массив, в котором соседние ячейки связаны друг с другом разрядными цепями передачи слов. Запись нового слова производится в верхнюю ячейку (ячейку 0), при этом все ранее записанные слова (включая слово, находившееся в ячейке 0), сдвигаются вниз, в соседние ячейки с большими на 1 номерами. Считывание возможно только из верхней (нулевой) ячейки памяти, при этом, если производится считывание с удалением, все остальные слова в памяти сдвигаются вверх, в соседние ячейки с большими номерами. В этой памяти порядок считывания слов соответствует правилу: последним поступил — первым обслуживается. В ряде устройств рассматриваемого типа предусматривается также операция простого считывания слова из нулевой ячейки (без его удаления и сдвига слова в памяти). Иногда стековая память снабжается счетчиком стека СчСт, показывающим количество

занесенных в память слов. Сигнал СчСт = 0 соответствует пустому стеку, СчСт = Ы—1 —заполненному стеку.

Обычно стековую память организуют, используя адресную память. В этом случае счетчик стека, как правило, отсутствует, так как количество слов в памяти можно выявить по указателю стека (см. гл. 8). Широкое применение стековая память находит при обработке вложенных структур данных.

В последующих параграфах описываются различные типы ЗУ с адресной организацией. В гл. 8 рассмотрено использование стековой памяти при выполнении безадресных команд и прерываний, а в гл. 14 — ассоциативной памяти в аппаратуре динамического распределения ОП.

Структуры адресных ЗУ

Техника оперативных памятей прошла большой путь развития. Большое значение имело появление в начале 50-х годов магнитных ЗУ, использующих в качестве запоминающего элемента (ЗЭ) ферритовые сердечники с прямоугольной петлей намагничивания. Магнитные ЗУ к настоящему времени вытеснены полупроводниковыми, в которых в качестве ЗЭ служат триг-герные схемы или МОП-транзисторы.

Тип используемых ЗЭ определенным образом влияет на структуру памяти, в результате чего существует большое разнообразие структур ЗУ. В настоящем параграфе дается систематизация структур адресных ЗУ1, что должно помочь пониманию принципов действия различных типов ЗУ с произвольным обращением и постоянных ЗУ.

Совокупность определенным образом соединенных ЗЭ образует запоминающую матрицу или запоминающий массив, где каждый ЗЭ хранит бит информации. Запоминающий элемент должен реализовать следующие режимы работы: хранение состояния, выдача сигнала состояния (считывание), запись 0 или запись 1. К ЗЭ должны поступать управляющие сигналы для задания режима работы, а также информационный сигнал при записи, а при считывании ЗЭ должен выдавать сигнал о его состоянии.

Запоминающий массив имеет систему адресных и разрядных линий (проводников). Адресные линии используются для выделения по адресу совокупности ЗЭ, которым устанавливается режим считывания или записи. Выделение отдельных разрядов осуществляется разрядными линиями, по которым передается

записываемая в ЗЭ информация или информация о состоянии ЗЭ.

Запоминающие устройства строятся из специфичных ЗЭ, для которых характерно использование троичных сигналов и совмещение линий входных и выходных сигналов.

Адресные и разрядные линии носят общее название линий выборки. В зависимости от числа таких линий, соединенных с. одним ЗЭ, различают двух- и трехкоординатные ЗУ и т. д., называемые ЗУ типа 2D, 3D и т. д. (от английского dimention— размерность). Наибольшее распространение получили ЗУ типа 2D, 3D, 2,5Dи их модификации.

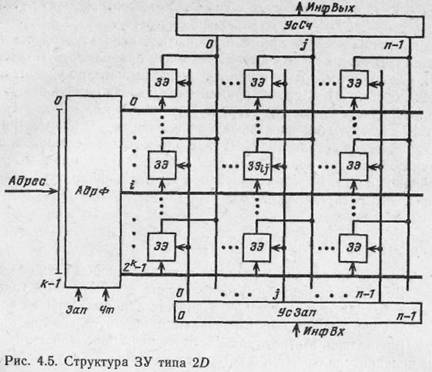

Запоминающие устройства типа 2D. Организация ЗУ типа 2D обеспечивает двухкоординатную выборку каждого ЗЭ ячейки памяти. Основу ЗУ составляет плоская матрица из ЗЭ, сгруппированных в 2* ячеек по п разрядов. Обращение к ячейке задается ^-разрядным адресом, выделение разрядов производится разрядными линиями записи и считывания. Структура ЗУ типа 2D приведена на рис. 4.5.

Адрес (^-разрядный) выбираемой ячейки iпоступает на схему адресного формирователя АдрФ, управляемого сигналами чтения Чт и записи Зап. Основу АдрФ составляет дешифратор с 2к выходами, который при поступлении на его входы адреса формирует сигнал для выборки линии i, при этом под воздействием сигналов Чт и Зап из АдрФ выдается сигнал, настраивающий ЗЭ i-й линии либо на считывание (выдачу сигнала состояния), либо на запись. Выделение разряда jв i-м слове производится второй координатной линией. При записи по линии jот усилителя записи УсЗап поступает сигнал, устанавливающий выбранный для записи 33;, в состояние 0 или 1. При считывании на усилитель считывания УсСч по линии / поступает сигнал о состоянии 3.9;,.

Используемые здесь ЗЭ должны допускать объединение выходов для работы на общую линию с передачей сигналов только от выбранного ЗЭ. Такое свойство типично для современных ЗЭ и в дальнейшем всякий раз подразумевается.

Таким образом, каждая адресная линия выборки ячейки передает три значения сигнала: выборка при записи, выборка при считывании и отсутствие выборки. Каждая разрядная линия записи передает в ЗЭ записываемый бит информации, а разрядная линия считывания — считываемый из ЗЭ бит информации. Линии записи и считывания могут быть объединены в одну при использовании ЗЭ, допускающих соединение выхода со входом записи. Совмещение функций записи и считывания на разрядной линии широко используется в современных полупроводниковых ЗУ.

Запоминающие устройства типа 2D являются быстродействующими и достаточно удобными для реализации. Однако ЗУ типа 2D неэкономичны по объему оборудования из-за наличия в них дешифратора с 2к выходами. В настоящее время структура типа 2D используется в основном в ЗУ небольшой емкости.

Запоминающие устройства типа 3D. Некоторые ЗЭ имеют не один, а два конъюнктивных входа выборки. В этом случае адресная выборка осуществляется только при одновременном появлении двух сигналов. Использование таких ЗЭ позволяет строить ЗУ с трехкоординатным выделением ЗЭ.

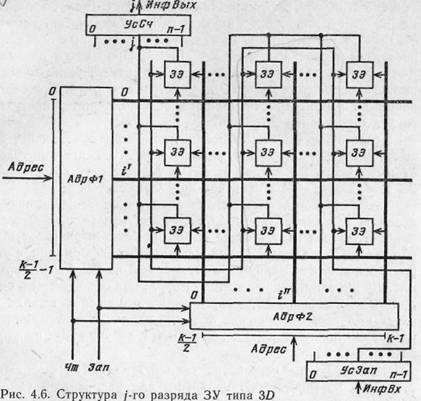

Запоминающий массив ЗУ типа 3D выполнен в виде пространственной матрицы, составленной из п плоских матриц, представляющих собой ЗМ для отдельных разрядов ячеек памяти. Запоминающие элементы для разряда сгруппированы в квадратную матрицу из \2к рядов по ~\j2kЗЭ в каждом.

Структура матрицы /-го разряда в ЗУ типа 3D представлена на рис. 4.6. Для адресной выборки ЗЭ задаются две его координаты в 3Mj. Код адреса i-й ячейки памяти разделяется на старшую и младшую части (i' и I"), каждая из которых поступает на свой адресный формирователь. Адресный формирователь АдрФ1 выдает сигнал выборки на линию ?, а АдрФ2 — на линию

i". В результате в 3Mjоказывается выбранным ЗЭ, находящийся на пересечении этих линий (двух координат), т. е. адресуемый кодом i=i'/i". Адресные формирователи управляются сигналами Чт и Зап. и в зависимости от них выдают сигналы выборки для считывания или записи. При считывании сигнал о состоянии выбранного ЗЭ поступает по /'-й линии считывания к УсСч (третья координата ЗЭ). При записи в выбранный ЗЭ будут занесены 0 и 1 в зависимости от сигнала записи в /-и разряд, поступающего по /-й линии от УсЗап (третья координата ЗЭ при записи). Для полупроводниковых ЗУ, как отмечалось выше, характерно объединение в одну линию разрядных линий записи и считывания.

Для построения «-разрядной памяти используется п матриц рассмотренного вида. Адресные формирователи при этом могут быть общими для всех разрядных ЗМ.

Запоминающие устройства типа 3D более экономичны, чем ЗУ типа 2D. Действительно, сложность адресного формирователя с mвходами пропорциональна 2т. Поэтому сложность двух адресных формирователей ЗУ типа 3D, пропорциональная 2'2*/2, значительно меньше сложности адресного формирователя ЗУ типа 2D, пропорциональной 2*. В связи с этим структура типа 3D позволяет строить ЗУ большего объема, чем структура 2D. Однако ЗЭ с тремя входами, используемыми при записи, не всегда удается реализовать.

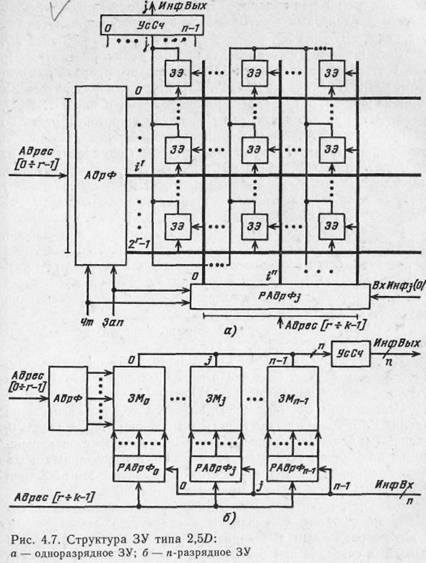

Запоминающие устройства типа 2.5D. В ЗУ этого типа при считывании состояния /-го разряда i-й ячейки положение ЗЭ(/-в ЗМ определяется тремя координатами (две координаты для

выборки и одна для выходного сигнала), а при записи в ЗЭ,, — двумя координатами. Считывание при этом осуществляется так же, как и в ЗУ типа 3D, а запись сходна с записью в ЗУ типа 2D.

Запоминающий массив ЗУ типа 2,5D можно рассматривать как состоящий из отдельных ЗМ для каждого разряда памяти: ЗМо, ЗМь • • •, ЗМ;,..., ЗМ..1. Структура одноразрядного ЗУ дана на рис. 4.7, а. Код адреса г'-й ячейки памяти, как и в ЗУ 3D, разделяется на две части: i' и i", каждая из которых отдельно дешифрируется. Адресный формирователь АдрФ выдает сигнал выборки на линию i', разрядно-адресный формирователь /-го разряда РАдрФ — на линию i". При считывании оба сигнала, являющиеся сигналами выборки для считывания, опрашивают ЗЭ, выходной сигнал которого поступает на УсСч разряда /. Работает ЗУ в этом случае так же, как и ЗУ типа 3D.

При записи АдрФ выдает сигнал выборки для записи, а РАдрФ выдает по линии I" сигнал записи 0 или 1 в зависимости от назначения входного информационного сигнала /-го разряда ВхИнФ,. На остальных линиях РАдрФ! не появляются сигналы записи, и состояния всех ЗЭ, кроме ЗЭ, лежащего на пересечении линий I' и i", не меняются.

Из ЗМ отдельных разрядов формируется ЗМ всего ЗУ согласно схеме на рис. 4.7, б.

Наиболее экономичным по расходу оборудования ЗУ оказывается в том случае, если число выходных линий АдрФ и всех РАдрФ равно, т.е. если r= (k— r) log2 п (рис. 4.7, б).

Недостатком ЗУ типа 2,5 D является то, что сигналы на линиях РАдрФ должны иметь четыре значения: чтение, запись О, запись 1 и отсутствие записи (хранение). Для ЗЭ с разрушающим считыванием сигналы чтения и записи 0 совпадают и потребуются лишь три значения сигнала. В связи с этим ЗУ типа 2,5D используется для ЗЭ с разрушающим считыванием.

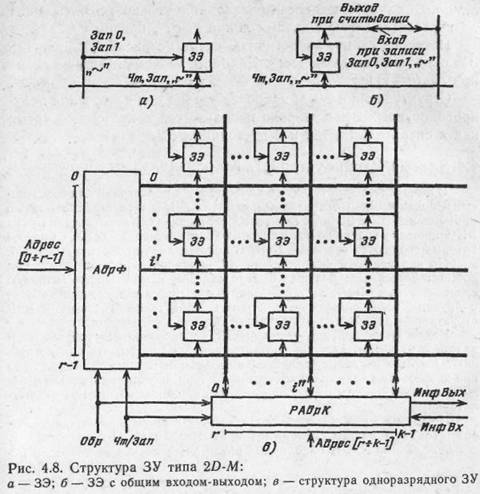

Для построения современных полупроводниковых ЗУ из ЗЭ с неразрушающим считыванием используется структура ЗУ с двухкоординатным выделением ЗЭ и мультиплексированием выходных сигналов при считывании. Такие ЗУ будем называть ЗУ типа 2D-M.

Запоминающие устройства типа 2D-M. Запоминающие элементы таких ЗУ имеют два входа и один выход (рис. 4.8, а). При наличии хотя бы одного пустого сигнала ~ на входах ЗЭ при записи находится в режиме хранения (как в ЗУ 3D). Сигнал чтения Чт опрашивает состояние ЗЭ (так же как и в ЗУ типа 2D). Сигналы записи Зап и Зап О устанавливают ЗЭ в состояние О, а Зап и Зап1 — в состояние 1 (так же, как и в ЗУ типов 2D и 2,5D).

Обычно у запоминающих элементов ЗУ типа 2D-Mвыход

объединяется со входом записи, как это показано для ЗЭ на рис. 4,8, б. Структура одноразрядного ЗУ типа 2D-M представлена на рис. 4.8, в. Как и в ЗУ типа 2,5 D, код адреса г'-й ячейки разделяется на две части: i' и i", одна из которых поступает на АдрФ, а другая — на разрядно-адресный коммутатор РАдрК. Если на АдрФ и РАдрК не приходит сигнал обращения к памяти Обр, то на их выходных линиях не возникают действующие на ЗЭ сигналы и все ЗЭ находятся в режиме хранения. При наличии сигнала Обр выполняется считывание или запись в зависимости от значения сигнала Чт/Зап. При считывании АдрФ выдает по линии /' сигнал выборки для считывания, по которому со всех ЗЭ линии i' сигналы их состояний поступают на РАдрК. Коммутатор РАдрК мультиплексирует эти сигналы и передает на выход ИнфВых сигнал с линии i". При записи АдрФ выдает по линии i' сигнал выборки для записи. Коммутатор РАдрФК в зависимости от значения ИнфВх выдает сигнал записи 0 или 1 на линию i" и сигналы, не воздействующие на ЗЭ, в остальные линии. В результате запись производится только в ЗЭ, лежащий на пересечении координатных линий i' и i"', причем i'/i" = L

Построив схему, аналогичную схеме на рис. 4.7, б, получим ЗУ для 2к п-разрядных ячеек. Наиболее экономична такая схема при r= (k— r) log2 п.

Структура типа 2D-Mнаиболее удобна для построения полупроводниковых ЗУ и широко используется в настоящее время как в оперативных, так и в постоянных ЗУ.

Запоминающие устройства с произвольным обращением

В вычислительной технике в качестве ЗУ с произвольным обращением, используемых в оперативных памятях ЭВМ, еще недавно широко применялись ЗУ с ЗЭ на ферритовых сердечниках. Успехи в технологии БИС привели к созданию полупроводниковых интегральных ЗУ, на основе которых создаются основные (оперативные) памяти современных ЭВМ.

По сравнению с ферритовыми ЗУ полупроводниковые имеют ряд важных достоинств: большее быстродействие, компактность, меньшую стоимость, совместимость по сигналам с логическими схемами, общие с другими электронными устройствами ЭВМ технологические и конструктивные принципы построения.

Недостатком полупроводниковых ЗУ с произвольным обращением является их энергозависимость, выражающаяся в том, что они потребляют энергию в режиме хранения информации и теряют информацию при выключении напряжения питания (потери информации можно избежать автоматическим переключением на аварийное питание от аккумуляторов) .

По типу ЗЭ различают биополярные ЗУ с биполярными транзисторами (с ТТЛ- или ЭСЛ-схемами) и МОП-ЗУ с МОП-транзисторами.

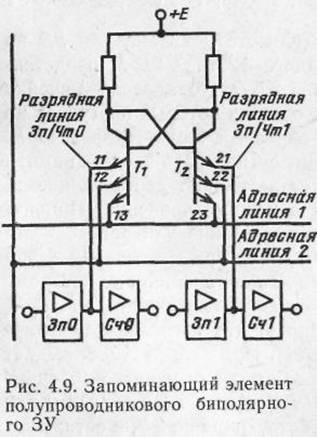

Биполярные ЗУ. В биполярных интегральных ЗУ в качестве ЗЭ используется статический триггер на двух многоэмиттерных транзисторах с непосредственными связями (рис. 4.9).

Эмиттеры // и 21 являются пара-фазными информационными входами ЗЭ и служат для записи в триггер 1 или 0. Эти же эмиттеры используются как выходы при считывании информации. Адресные эмиттеры 12, 22, 13 и 23 образуют два конъюнктивно связанных входа выборки.

Организация ЗУ из триггеров осуществляется по схеме типа 3D.

В режиме хранения (ЗЭ не выбран) эмиттерный ток открытого транзистора замыкается на землю через адресные эмиттеры и адресные линии (или только через один такой эмиттер и одну линию), находящиеся под потенциалом логического 0 (<0,4В). При этом информацион-

ные эмиттеры должны быть заперты, для чего на них подается потенциал (1 — 1,5В), который больше потенциала адресных эмиттеров (больше максимального значения уровня сигнала логического 0, равного 0,4 В, но меньше-минимального значения сигнала логической 1, составляющего 2,4 В), с тем чтобы при выборке ЗЭ через информационные эмиттеры протекали токи, необходимые для операций считывания и записи.

При выборке данного ЗЭ на его адресные эмиттеры с выходов адресных дешифраторов подается потенциал логической 1 (^2,4 В), превышающий потенциал информационных эмиттеров. Поэтому адресные эмиттеры оказываются запертыми, а коллекторный ток открытого транзистора течет через его информационный эмиттер, чем обеспечивается возможность считывания из ЗЭ и записи в него информации.

Состояния 1 и 0 ЗЭ распознаются по наличию тока соответственно в разрядной линии 0 (открыт транзистор Т\) или в разрядной линии 1 (открыт транзистор Г2)-

Считывание происходит без разрушения информации. Хранимая в ЗЭ информация доступна для считывания все время, пока ЗЭ находится в выбранном состоянии, и в него не производится запись (отсутствует импульс «разрешение записи»).

При считывании на входы обоих усилителей записи подается потенциал логического 0, в результате чего на выходах этих усилителей оказывается потенциал логической 1, запирающий усилители записи и тем самым предотвращающий ответвление в них тока считывания (тока информационного эмиттера).

При считывании ток вытекает из информационного эмиттера открытого транзистора и втекает в базовую цепь входного транзистора соответствующего усилителя считывания, в результате чего выходной транзистор последнего полностью открывается.

Для записи в ЗЭ 1 или 0 с соответствующего усилителя записи на подключенный к нему информационный эмиттер подается потенциал логического 0 (^0,4 В), а на другой информационный эмиттер продолжает поступать с его невозбужденного усилителя записи потенциал, равный примерно 1,5 В.

Если допустим, производится запись 1 в триггер, находившийся перед этим в состоянии 1 (открыт транзистор Т%), то подача потенциала низкого уровня на эмиттер 21 не меняет состояние триггера. Если до записи триггер находился в состоянии 0, то при подаче потенциала низкого уровня на эмиттер 21 (запись 1) открывается транзистор Гг, при этом транзистор Т\ закрывается и триггер устанавливается в состояние 1.

Интегральная микросхема биполярного ЗУ представляет собой кристалл кремния, в котором образованы массив ЗЭ (триггеров) со всеми межсоединениями, а также адресные дешифраторы, усилители-формирователи записи и считывания и другие схемы для управления адресной выборкой, записью и считыванием. Для повышения быстродействия ЗУ эти обслуживающие схемы могут быть выполнены на основе ЭСЛ-элементов, работающих в линейной области, в то время как построенные на основе ТТЛ-элементов триггеры ЗЭ работают с насыщением. В таком случае кристалл содержит схемы согласования уровней сигналов для перехода от схем ТТЛ к схемам ЭСЛ и обратно.

Полупроводниковые ЗУ размещаются в стандартных корпусах интегральных микросхем. Число выводов ограничивают число слов и разрядов запоминающего массива интегральной микросхемы. Для получения ЗУ с большим числом разрядов и (или) слов, чем в запоминающем массиве в корпусе схемы, применяются несколько корпусов.

В настоящее время биполярные ЗУ довольно дороги, поэтому они используются главным образом в качестве сверхоперативных памятей.

Динамические МОП-ЗУ сравнительно дешевы, потребляют небольшую мощность, позволяют достигнуть очень высокой плотности размещения ЗЭ на кристалле и, следовательно, большей емкости в одном корпусе микросхемы. В настоящее время динамические МОП-ЗУ широко используются для построения основной (оперативной) памяти ЭВМ.

В динамических ЗУ двоичные коды хранятся на «запоминающих емкостях», в качестве которых используются паразитные емкости некоторых цепей схем. Примем, что отсутствие заряда на запоминающей емкости означает состояние 0, а наличие — состояние 1. В таком случае считывание информации состоит в определении, заряжены или нет запоминающие емкости.

Запоминающая емкость может неопределенно долго сохранять состояние 0 (разряд отсутствует), но только ограниченное время из-за утечки заряда — состояние 1. Поэтому в рассматриваемых ЗУ необходимо периодически (примерно через каждые 2 мс) производить восстановление хранимой информации. Операция динамического восстановления информации называется рефреш. Рассматриваемые ЗУ получили название динамических.

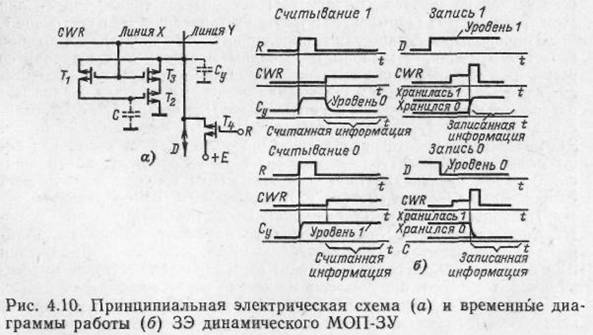

Схема и временные диаграммы работ ЗЭ динамического ЗУ на МОП-транзисторах в памяти со структурой 2D-Mпредставлены на рис. 4.10. Запоминающей емкостью служит паразитная емкость С затвора транзистора Т%. Линия разрядно-адресного коммутатора Yиспользуется для ввода в ЗЭ бита информации при записи и съема его при считывании (см. рис. 4.8). Так как ЗЭ использует источник питания только при считывании, то им может служить паразитная емкость Су линии Y.

Предварительно перед считыванием от разрядно-адресного коммутатора подается сигнал R, с помощью которого подготавливается считывание с мультиплексированием для ЗЭ, выбираемых линией разрядно-адресного формирователя. Сигнал Rоткрывает транзистор Г4, и емкость Су подзаряжается от источника. Затем на линию Xподается от адресного формирователя сигнал считывания — промежуточный уровень сигнала CWR, который открывает транзистор Гз, но не может открыть Гг. Если ЗЭ хранит 1, то конденсатор С заряжен и открыт транзистор Гг. В этом случае через открытые транзисторы Гз и Г2 конденсатор Су разряжается

и низкий уровень (уровень 0) сигнала Dна линии Yуказывает, что ЗЭ хранил инверсное значение, т.е. 1. Если ЗЭ хранит 0, то емкость С разряжена, Г2 закрыт и сигнал CWRне может вызвать разряд емкости Сг Высокий уровень сигнала D(уровень 1) указывает, что ЗЭ хранил 0. Далее сигнал Dчерез разрядно-адресный коммутатор поступает на выход ЗУ.

При записи на линию Yпоступает сигнал D, соответствующий записываемому двоичному знаку. Затем на линию Xподается высокий уровень сигнала CWR, открывающий транзистор Т\, который подключает к линии Yконденсатор С. В результате независимо от своего предыдущего состояния емкость оказывается заряженной, если записывается 1, и разряженной, если записывается 0.

В ЗУ периодически производится регенерация информации. При регенерации в ЗЭ записывается инверсное значение хранимого до считывания кода. После каждой четной регенерации — его инверсия. В ЗУ имеется схема, сигнал которой указывает, какой код хранить в данный момент ЗЭ — прямой или инверсный.

В настоящее время большие оперативные памяти ЭВМ выполняют главным образом на динамических МОП-ЗУ, небольшие ОП — на МОП-ЗУ и ТТЛ-ЗУ, а сверхоперативные и буферные памяти — на ЭСЛ-ЗУ и ТТЛ-ЗУ.

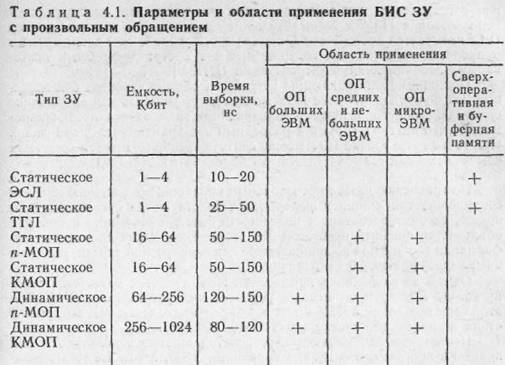

В табл. 4.1 приведены характерные параметры БИС для разных типов полупроводниковых ЗУ и указаны области их использования.

Постоянные ЗУ

Постоянные запоминающие устройства (ПЗУ) в рабочем режиме ЭВМ допускают только считывание хранимой информации. В зависимости от типа ПЗУ занесение в него информации производится в процессе или изготовления, или эксплуатации путем настройки, предваряющей использование ПЗУ в вычислительном процессе. В последнем случае ПЗУ называется постоянным запоминающим устройством с изменяемым в процессе эксплуатации содержимым или программируемыми постоянными запоминающими устройствами (ППЗУ).

Постоянные запоминающие устройства обычно строятся как адресные ЗУ. Функционирование ПЗУ можно рассматривать как выполнение однозначного преобразования ^-разрядного кода адреса ячейки запоминающего массива (ЗМ) в n-разрядный код хранящегося в ней слова. При такой точке зрения ПЗУ можно считать преобразователем кодов или комбинационной схемой (автоматом без памяти) с kвходами и п выходами.

По сравнению с ЗУ с произвольным обращением, допускающим как считывание, так и запись информации, конструкции ПЗУ значительно проще, их быстродействие и надежность выше, а стоимость ниже. Это объясняется большей простотой ЗЭ, отсутствием цепей для записи информации вообще или по крайней мере для оперативной записи, реализацией неразрушающего считывания.

Одним из важнейших применений ПЗУ является хранение микропрограмм в микропрограммных управляющих устройствах ЭВМ. Для этой цели необходимы ПЗУ значительно большего, чем в ОП, быстродействия и умеренной емкости (10 000—100 000 бит).

Постоянные запоминающие устройства широко используются для хранения программ в специализированных ЭВМ, в том числе в микро-ЭВМ, предназначенных для решения определенного набора задач, для которых имеются отработанные алгоритмы и программы, например в бортовых ЭВМ самолетов, ракет и космических кораблей, в управляющих вычислительных комплексах, работающих в АСУ технологическими процессами. Такое применение ПЗУ позволяет существенно снизить требования к емкости ОП, повысить надежность и уменьшить стоимость вычислительной установки.

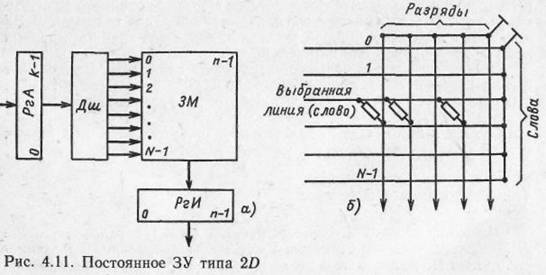

На рис. 4.11, а приведена схема простейшего ПЗУ со структурой типа 2D. Запоминающий массив образуется системой взаимно перпендикулярных линий, в их пересечениях устанавливаются ЗЭ, которые либо связывают (состояние 1), либо не связывают (состояние 0) между собой соответствующие горизонтальную и вертикальную линии. Поэтому часто ЗЭ и ПЗУ называют связывающими элементами. Для некоторых типов ЗЭ состояние 0 означает просто отсутствие запоминающего (связывающего) элемента в данной позиции в ЗМ.

Дешифратор Дш по коду адреса в РгА выбирает одну из горизонтальных линий (одну из ячеек ЭВМ), в которую подается сигнал выборки. Выходной сигнал 1 появляется на тех вертикальных разрядных линиях, которые имеют связь с возбужденной адресной линией (на рис. 4.11,6 считывается слово 11010).

В зависимости от типа запоминающих (связывающих) элементов различают резисторные, емкостные, индуктивные (трансформаторные), полупроводниковые (интегральные) и другие ПЗУ.

В настоящее время наиболее распространенным типом являются полупроводниковые интегральные ПЗУ.

Полупроводниковые интегральные ПЗУ. Полупроводниковые ПЗУ имеют все те же достоинства, которые отмечались в предыдущем параграфе в отношении полупроводниковых ЗУ с произвольным обращением. Более того, в отличие от последних они являются энергонезависимыми. Постоянные ЗУ имеют большую емкость на одном кристалле (в одном корпусе интегральной микросхемы).

Положительным свойством интегральных ПЗУ является то, что некоторые типы этих устройств позволяют самому потребителю производить их программирование (занесение информации) в условиях эксплуатации и даже многократное перепрограммирование.

По типу ЗЭ, устанавливающих или разрывающих связь (контакт) между горизонтальными и вертикальными линиями, различают биполярные и МОП-схемы ПЗУ. Биполярные ПЗУ имеют время выборки 30— 50 нс и емкость в одном кристалле (корпусе) от 256 бит до 16 Кбит. Постоянные маскируемые ЗУ на МОП-схемах имеют большую емкость в одном кристалле (корпусе) — до 64 Кбит и более, но и значительно меньшее быстродействие: время выборки 100—200 не.

По важнейшему признаку — способу занесения информации — реализуют три типа интегральных полупроводниковых ПЗУ: 1) с программированием в процессе изготовления путем нанесения при помощи фотошаблонов в нужных потребителю точках контактных перемычек; 2) с программированием выжиганием перемычек или пробоем р-п-пере-ходов, с помощью которых сам потребитель уже после изготовления прибора может уничтожить или образовать связи между горизонтальными и вертикальными линиями ЗМ (одноразовое программирование);

3)

с электрическим перепрограммированием, при котором информация заносится в ЗМ электрическим путем, а стирание информации, необходимое для изменения содержимого ПЗУ, выполняется воздействием на ЗМ ультрафиолетового излучения или электрическим путем (многократное программирование).

Программируемые фотошаблонами и выжиганием ПЗУ могут строиться на основе как биполярных, так и МОП-схем. Перепрограммируемые ПЗУ используют только МОП-схемы, способные хранить заряды.

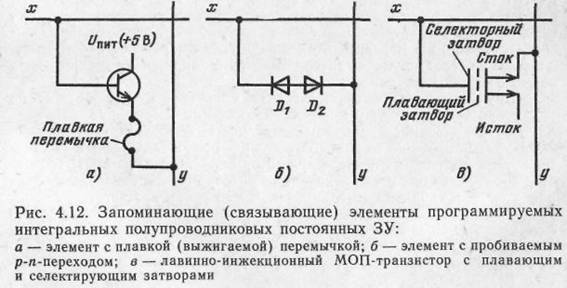

Различные типы ЗЭ интегральных ПЗУ представлены на рис. 4.12. На рис. 4.12, а показан биполярный транзисторный ЗЭ с выжигаемой перемычкой, соединяющий горизонтальную и вертикальную линии. При «программировании» ПЗУ перемычки выжигаются в нужных местах серией импульсов тока с амплитудой 20—30 мА. При выборе адресным дешифратором горизонтальной линии х на базу транзистора ЗЭ поступает открывающий его сигнал, и при наличии перемычки (состояние 1) на вертикальной линии у появится потенциал коллектора транзистора +5 В.

На рис. 4.12, б изображен ЗЭ, программируемый пробиванием p-n-перехода. В исходном состоянии включенные встречно диоды изолируют линии х и у (состояние 0). При подаче повышенного напряжения диод Diпробивается и закорачивается (состояние 1).

Более просто устроены ПЗУ с транзисторными и диодными запоминающими (связывающими) элементами, программируемые при изготовлении ПЗУ. В этом случае с помощью фотошаблонов в нужных позициях ЗМ наносятся или не наносятся контактные перемычки (вместо плавкой перемычки и вместо диода Ј>i на рис. 4.12, а и б соответственно).

На рис. 4.12, б представлен ЗЭ в виде лавинно-инжекционного МОП-транзистора с плавающим и селектирующим затворами. Интегральные ПЗУ на таких элементах допускают многократную замену хранимой информации.

' Плавающий (изолированный) затвор не имеет электрического подвода, он предназначен Для хранения заряда. Селектирующий затвор подсоединен к одному из выходов дешифратора строк — горизонтальной линии, а сток — к вертикальной линии. В исходном состоянии отсутствует заряд на плавающем затворе (состояние 1), транзистор имеет очень небольшое пороговое напряжение. Выбор элемента осуществляется путем подачи на селектирующий затвор выходного напряжения адресного дешифратора, при этом включается транзистор и через цепь сток — исток протекает значительный ток. Программирование (занесение 0 в элементы) производится подачей на сток импульса напряжения 25—50 В, при этом происходит инжекция электронов, имеющих высокую энергию, через оксид на изолированный затвор, получающий отрицательный заряд (состояние 0). В результате увеличивается пороговое напряжение, и подача на селектирующий затвор выходного напряжения дешифратора не включает этот транзистор.

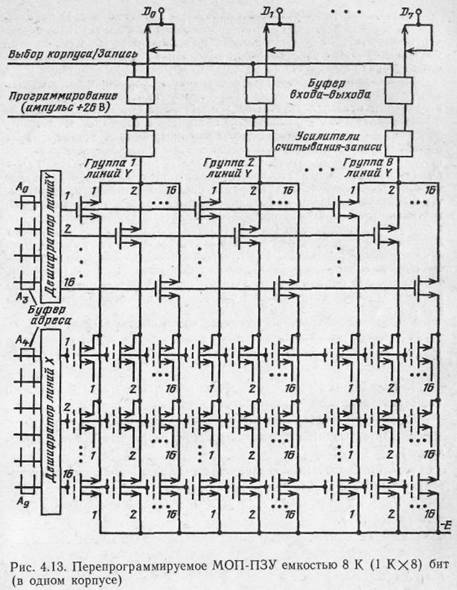

Структура программируемого ПЗУ емкость 8 К (1 КХ8) бит на одном кристалле (в одном корпусе) изображена на рис. 4.13.

Рассматриваемое перепрограммируемое ПЗУ имеет структуру типа 2D-M. Запоминающий массив содержит 64 горизонтальных Xи 128 вертикальных Yлиний, на пересечении которых расположены МОП-транзисторы с плавающим и селектирующим затворами. Вертикальные линии разбиты на 8 групп по 16 в каждой. Число групп соответствует числу разрядов, хранимых в микросхеме (корпусе) слов. В качестве адресного формирователя используется дешифратор линий X, выдающий сигналы чтения. Разрядно-адресный коммутатор образован дешифратором линий Y, который управляет коммутирующими транзисторами, подсоединенными к разрядным усилителям считывания-записи.

При подаче младших разрядов адреса Л4—Л9 на дешифратор линий Xвыбирается одна из 64 горизонтальных линий, в результате чего управляющий потенциал поступает на присоединенные к ней линии, селектирующие затворы 128 ЗЭ. В каждой группе линий по коду старших разрядов адреса А0—Л3 мультиплексируются сигналы от выбранных ЗЭ и выделяется сигнал адресуемого ЗЭ. Разрядные усилители формируют его и через буфера входа-выхода выдают на выходы Da—Diмикросхемы сигналы логических 0 и 1, соответствующие информации, находящейся в выбранной ячейке. При считывании информация в ячейке сохраняется

Рассматриваемое ПЗУ может работать в двух режимах: 1) считывание хранимой информации и 2) программирование (запись) ПЗУ. Режим считывания устанавливается подачей сигнала выбора корпуса, который настраивает схемы буферов входа-выхода и разрядных усилителей на формирование и передачу на выходы Do—Diсигналов, считанных с ЗЭ.

Перед записью производится стирание информации воздействием ультрафиолетового света через окно в корпусе микросхемы на полупроводниковый кристалл ПЗУ. Под воздействием света заряды стекают с затворов. После стирания все ЗЭ находятся в состоянии 1.

Режим записи осуществляется при одновременной подаче сигнала Запись и импульса Программирование. На входы корпуса Аа—Лд поступает адрес ячейки, в которую производится запись, а на выходы Do— D7 (в режиме записи ставшие входами) записываемое 8-разрядное слово. Сигнал Запись настраивает буфера входа-выхода и разрядные усилители на передачу информационных сигналов со входов Do—Djк стокам ЗЭ, при этом открываются усилители записи тех разрядов, в которых в записываемом слове находятся 0. Эти усилители пропускают в выбранные дешифратором линий У вертикальные линии импульс Программирование (импульс +26 В), который обеспечивает лавинный пробой и занесение отрицательного заряда в плавающие затворы (запись 0) только тех ЗЭ, селектирующие затворы которых присоединены к горизонтальной линии, возбужденной выходным сигналом дешифратора линий X.

Рассматриваемое устройство имеет время выборки 0,4—1 мкс. |