Микросхема КР1810ГФ84

Микросхема КР1810ГФ84 представляет собой тактовый генератор и задающее устройств для микропроцессора КМ1810ВМ86. Ее значение — формирование тактовых сигналов для микропроцессора и периферийных устройств, а также сигналов «Установка» и «Готовность».

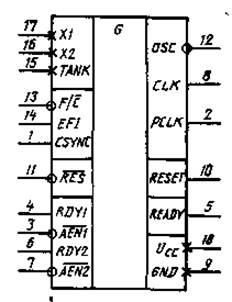

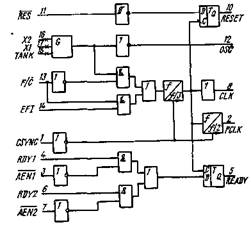

Условное графическое обозначение микросхемы приведено на рис. 1, назначение выводов — в табл. 1, функциональная схема показана на рис. 2.

Микросхема состоит из следующих функ1иональных узлов: задающего мультивибратора, делителей на 2 и на 3, формирователя тактового сигнала, схем синхронизации и выбора задающей частоты и схем формирования сигналов «Установка» и «Готовность».

|

Рис 1 |

Таблица 1

Вывод |

Обозначение |

Thii вывода |

Функциональное назначение выводов |

1 |

CSYNC |

Вход |

Синхронизация |

2 |

PCLK |

Выход |

Периферийный тактовый сигнал ТТЛ |

3 |

AEN1 |

Вход |

Адрес готовности шины 1 |

4 |

\RDY1 |

Вход |

Сигнал готовности шины 1 |

5 |

READY |

Выход |

Готовность |

6 |

RDY2 |

Вход |

Сигнал готовности шины 2 |

7 |

AEN2 |

Вход |

Адрес готовности шины 2 |

8 |

CLK |

Выход |

Тактовый сигнал МОП |

9 |

GND |

— |

Общий |

10 |

RESET |

Выход |

Установка |

11 |

~RES |

Вход |

Сигнал установки |

12 |

OSC |

Выход |

Мультивибратор |

13 |

F/C~ |

Вход |

Выбор источника частоты |

14 |

EF1 |

Вход |

Внешняя частота |

15 |

TANK |

— |

Вывод подключения LC-контура |

16, 17 |

X2, XI |

— |

Выводы подключения резонатора |

18 |

Ucc |

— |

Напряжение питания |

В качестве источника частоты в микросхеме используется кварцевый резонатор, подключаемый к выводам XI и Х2 мультивибратора (при этом на входе F/Cдолжен быть сигнал низкого уровня), либо внешний ТТЛ-сигнал, поступающий на вход EFI(на входе F/Cсигнал высокого уровня). Выбранный источник должен генерировать на трехкратной частоте тактового сигнала CLK, требуемой для микропроцессора.

При использовании кварцевого резонатора возможна работа на его гармониках. В этом случае к выводу TANKподключается резонансный Z-C-контур.

|

Рис 2 |

Однако стабильность тактовой частоты обеспечивается только при работе на основной частоте резонатора. Резонатор следует располагать в непосредственной близости от выводов микросхемы XIи Х2 с обеспечением минимального сопротивления соединяющих проводников. Рекомендуемые типы резонаторов: РГ-05, РК8, РК45ММ и другие, имеющие металлический корпус н малые габаритные размеры. Последовательно с резонатором подключается конденсатор небольшой емкости (5—25 пФ), подбираемый при точной настройке иа требуемую частоту мультивибратора.

При использовании внешнего генератора скважность импульса сигнала EFIдолжна быть близка к 2, частота — не более 25 МГц.

В микросхеме КР1810ГФ84 имеется три частотных выхода: OSC—мультивибратор, CLK - тактовый сигнал МОП н PCLK - периферийный тактовый сигнал ТТЛ.

Выход OSCможет подключаться к другим генераторам КР1810ГФ84 в качестве источника внешней частоты. Сигнал OSCиспользуется также для тактирования схемы управления динамическим ОЗУ. Сигнал OSCинвертирован по отношению к сигналу мультивибратора, управляющему тактовым сигналом CLK. Скважность импульса OSCравна 2.

Тактовын сигнал CLKобразуется путем деления на три частоты мультивибратора или EFIСкважность импульса CLKравна 3, амплитуда около 4,5 В (при Ucc = 5,0 В), длительность фронта (среза) менее 10 не. Перечисленные параметры тактового сигнала необходимы для эффективного управления микропроцессором, другими МОП- и ТТЛ- устройствами, непосредственно соединенными с местной процессорной шиной.

Периферийный тактовый сигнал PCLKобразуется путем деления на 2 частоты сигнала CLK. Он предназначен для тактирования различных периферийных устройств, работающих на уровнях сигнала ТТЛ. Скважность импульса PCLKравна 2.

Схема синхронизации предназначена для совместной работы нескольких 1енераторон КР1810ГФ84 либо для синхронизации генератора с внешним источником частоты. Если на входе CSYNC— сигнал высокого уровня, то делители «а 2 и на 3 выключены и на выходах CLKи PCLK— сигнал высокого уровня. Ксли на входе CSYNC— сигнал низкого уровня, то на выходах CLKи PCLKпроисходит генерирование с частотами, соответственно в 3 и 6 раз меньшими частоты OSCили EFI.

Схема формирования сигнала «Установка» состоит из триггера Шмидта и D-триггера, тактируемого отрицательным перепадом импульса CLK. Сигнал «Установка» на выходе RESETинвертируется по отношению к входному сигналу RES. Повышенное пороговое напряжение высокого уровня на входе RESобеспечивает необходимое время установки процессора.

Таблица 2

Параметр |

Обозначение |

Значения мин . |

la pa метров макс. |

Напряжение питания, В |

1 "ее |

4 ,75 |

5,25 |

Входное напряжение низкого уровня, В Входное напряжение высокого уровня, В: |

U,L |

— |

0,8 |

для входа RES |

|

2,6 |

5,25 |

для остальных входов |

U ,н |

2,0 |

5,25 |

Выходной ток низкого уровня, мА |

I л 'oL |

_ |

5,0 |

Выходной ток высокого уровня, мА |

|

— |

—1 ,0 |

Емкость нагрузки, пФ: выхода CLK |

CL, CLK |

— |

100 |

|

с. |

.— |

30 |

Длительность фронта (среза) входного импульса, не: |

|

|

|

для входа EFI |

*LH Chl> |

|

5(5) |

для входа RES |

|

He orpаничена |

для остальных входов |

. |

18(18)** |

|

иа входе EFI, не |

WL, EFn'WH, EFI) |

|

|

Частота генерирования иа выходе OSC, МГц |

fosc |

|

25 |

Частота следования импульсов на входе EFI, МГц |

fEFI |

|

25 или |

|

|

|

1EFI >

>40 не |

Таблица 3

Параметр |

Обозначение |

Значения параметров [мин. (макс .)] |

Лериод следования импульсов тактового сигнала CLK, не |

ТС1.К |

125(500) |

Зремя установления сигналов RDYJ, RDY2 относительно сигнала CLK, не |

fSU(CLK~RDY) |

35 |

Время сохранения сигналов RDY1. RDY2 относительно сигнала CLK, не |

lV(CLK- RDY) |

0 |

Зремя установления сигналов AENI, AEN2 относительно сигналов RDY1, RDY2 соответственно, не |

lSV{RDY -JET.) |

15 |

Зремя сохранения сигналов AENI, AEN2 относительно сигнала CLK, не |

h^CLK-AEN) |

0 |

Зремя установления сигнала CSYNCотносительно сигнала EFI, не |

tS\J(EFl —CSYNC) |

20 |

Время сохранения сигнала CSYNCотносительно сигнала |

tvt.EFl -CSYNC) |

20 |

Длительность сигнала высокого уровня на входе CSYNC, не |

'\VH, CSYSC |

27-£Р/ |

Время установления сигнала RESотносительно сигнала CLK, не |

'SU(CLK RES) |

65* |

Зремя сохранения сигнала RESотносительно сигнала CLK. не |

lV {CLK -RES) |

20* |

|

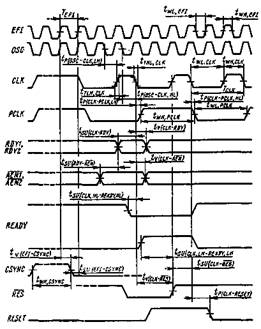

Рис 3 |

Схема формирования сигнала «Готовность» содержит логическую схему и D-триггер, также тактируемый отрицательным перепадом импульса CLK. Сигналы RDY, поступающие от двух системных шин, являются сообщением о наличии информации и подтверждаются соответствующими сигналами AEN. Готовность системы осуществляется синхронно с тактовым сигналом.

Временная диаграмма работы микросхемы КР1810ГФ84 приведена на рис. 16.31, основные параметры даны в табл. 16.29, предельно допустимые электрические режимы эксплуатации — в табл. 16.30, предельные значения режимов эксплуатации — в табл. 16.22. В табл. 16.31 указаны временные параметры, рекомендуемые для эксплуатации и обеспечивающие устойчивую работу системы в целом.

Примеры использования микросхемы КР1810ГФ84 приведены на рис. 16.23—16.25, на которых показаны различные варианты формирования сигнала «Готовность» при работе с одной и двумя системными шинами. Сигнал подтверждения передачи данных ХАСК является для микросхемы КР1810ГФ84 сигналом готовности шины RDY, а сигнал разрешения доступа к системной шине, поступающий от арбитра КР1810ВБ89,— адресом готовности AEN.

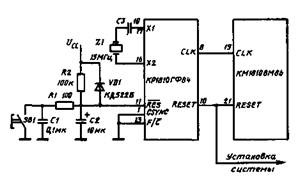

Установка системы в исходное состояние может осуществляться при включении питания с помощью простой RС-цепи, подключаемой к входу RES, либо при нажатии кнопки в дистанционной схеме управления, изображенной на рис. 16.32.

|

Рис 4 |

В небольших однопроцессорных высокопроизводительных системах, состоящих из нескольких устройств, используют минимальный режим. В сложных одно- или многопроцессорных высокопроизводительных 8- или 16-раз |