Микросхема КМ1810ВМ86

Микросхема КМ1810ВМ86 представляет собой однокристальный высокопроизводительный 16-разрядный микропроцессор с фиксированной системой команд. Она предназначена для использования в качестве центрального процессорного устройства при построении средств вычислительной техники — от простейших одноплатных микро-ЭВМ до высокопроизводительных мультипроцессорных систем.

Микропроцессор обладает высоким быстродействием (до 2,5-106 операций/с типа RRпри тактовой частоте 5 МГц), обеспечивает возможность прямой адресации памяти объемом до 1М байта, 65536 устройств ввода и 65536 устройств вывода. Для вычисления адресов операндов, размещенных в памяти, используется 24 режима адресации. Микропроцессор имеет векторную структуру прерывания и обеспечивает обработку до 256 запросов прерывания трех типов: внешних, внутренних и программных.

Архитектурной особенностью микропроцессора КМ1810ВМ86 является наличие аппаратно-программных средств, позволяющих упростить построение мультипроцессорных систем на его основе. Эти средства обеспечивают синхронизацию работы нескольких независимых (выполняющих собственные потоки команд) процессоров, имеющих общие ресурсы, а также синхронизацию параллельной работы микропроцессора и сопроцессоров (специализированных процессоров, аппаратно реализующих команды сложных процедур). Микропроцессор К.М1810ВМ86 характеризуется двумя режимами работы — минимальным и максимальным, которые отличаются способом формирования сигналов обмена и соответственно возможностями реализуемых систем.

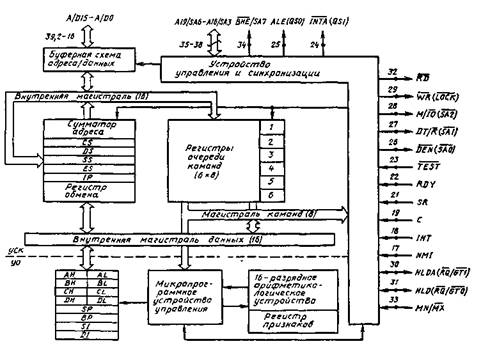

Условное графическое обозначение микросхемы приведено на рис. 1, назначение выводов, используемых как для минимального, так и максимального режимов работы, — в табл. 1, назначение выводов, используемых только в минимальном режиме или только в максимальном режиме, в табл. 2, структурная схема показана на рис. 2.

Структура микропроцессора К.М1810ВМ86 ориентирована на параллельное выполнение функций выборки и команд; состоит из устройства сопряжения канала (УСК), обработки (УО) и устройства управления и синхронизации.

Таблица 1

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

1, 20 |

GND |

|

Общий |

2-16, |

A/D0— |

Вход/ |

Канал адреса/данных |

39 |

A/D15 |

выход |

|

17 |

NMI |

Вход |

Немаскируемый запрос прерывания |

18 |

INT |

Вход |

Маскируемый запрос прерывания |

19 |

С |

Вход |

Тактовый сигнал |

21 |

SR |

Вход |

Сигнал «Установка» |

22 |

RDY |

Вход |

Сигнал «Готовность» |

23 |

TEST |

Вход |

Сигнал «Проверка» |

32 |

RD |

Выход |

Сигнал «Чтение» |

33 |

MN MX |

Вход |

Режим минимального максимального включения |

34 |

BHE/SA7 |

Выход |

Разрешение передачи по старшей половине канала данных D15—DS/сигнал состояния |

35—38 |

A19/ SA6; A18/SA5; A17/SA4; A16 /SA3 |

Выходы |

Канал адресa сигналы состояния |

40 |

Ucc |

— |

Напряжение питания +5 В |

Таблица 2

Вывод |

Обозначение |

Tиii вывода |

Функциональное назначение выводов |

|

Режим |

минимального в |

ключения микросхемы |

24 |

INTA |

Выход |

Подтверждение прерывания |

25 |

ALE |

Выход |

Стробирующий сигнал адреса |

26 |

DEN |

Выход |

Разрешение передачи данных |

27 |

DT R |

Выход |

Выдача прием данных |

28 |

M/10 |

Выход |

Память/внешнее устройство |

29 |

WR |

Выход |

Запись |

30 |

Hl.DA |

Выход |

Подтверждение захвата |

31 |

HLD |

Вход |

Захват |

|

Режим |

максимального в |

ключения микросхемы |

24, 25 |

QS1, QSO |

Выходы |

Сигналы состояния очереди команд |

26-28 |

SA0—SA2 |

Выходы ' |

Сигналы состояния цикла канала |

29 |

LUCK |

Выход |

Канал занят |

30, 31 |

rq/gtJ, rq gt0 |

Вход выход |

Запрос разрешение доступа к магистрали |

|

Рис 2 |

Устройство сопряжения канала предназначено для: формирования физического адреса памяти, выборки команд из памяти и записи их в очередь команд, чтения операндов команд из памяти или регистров ввода/вывода, записи результатов выполнения команд в память или регистры ввода/вывода.

В УСК входят: шесть 8-разрядных регистров очереди команд; четыре 16-разрядных сегментных регистра; 16-разрядный регистр адреса (указателя) команды; 16-разрядный регистр обмена; 16-разрядный сумматор адреса.

Устройство обработки предназначено для выполнения операций по обработке данных. Команды, выбранные из памяти и записанные в регистры очереди команд УСК, по запросам от УО поступают через 8-разрядную магистраль команд на микропрограммное устройство управления, которое декодирует команды и вырабатывает соответствующую последовательность микрокоманд, управляющую процессом выполнения текущей операции. УО не имеет непосредственной связи с внешней магистралью системы и обменивается данными через регистр обмена с УСК.

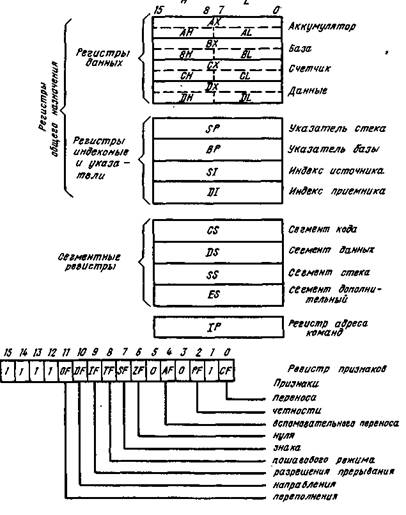

В устройство обработки входят: 16-разрядное арифметико-логическое устройство, восемь 16-разрядных регистров общего назначения, 16-разрядный регистр признаков состояния микропроцессора. Программно-доступными функциональными частями микропроцессора являются регистры общего назначения, сегментные регистры, регистр адреса (указателя) команд и регистр признаков (рис. 16.3).

Регистры общего назначения используются для хранения операндов и результатов выполнения команд и делятся на две группы: регистры данных, индексные регистры н указатели.

В группу регистров данных входят: регистр аккумулятора АХ; регистр указателя базы данных ВХ, регистр счетчика циклов СХ, регистр данных DX.

В группу индексных регистров и регистров указателей входят: регистр указателя стека SP, регистр указателя базы стека ВР, регистр индекса источника 5/, регистр индекса приемника DI.

Старшие и младшие восемь разрядов группы регистров данных могут быть адресованы раздельно. Они образуют набор 8-разрядиых регистров общего назначения (АН, AL, ВН, BL, CH, CL, DH, DL), причем регистрам АН, ВН, CH, DHсоответствуют старшие восемь разрядов, а регистрам AL, BL, CL, DL— младшие восемь разрядов группы регистров данных.

Сегментные регистры используются для организации сегментной адресации памяти н предназначены для хранения базовых адресов текущих сегментов памяти. В КМ1810ВМ86 имеется четыре 16-разрядных сегментных регистра: кода CS, данных DS, стека 55, дополнительного сегмента ES.

Разряды регистра признаков содержат признаки состояния микропроцессора, которые разделены на две группы: признаки результата и признаки управления.

В группу признаков результата входят:

признак переполнения OF, указывающий на переполнение в случае выполнения операций над целыми числами;

признак знака SF, указывающий на знак результата;

признак нуля ZF, указывающий на равенство нулю результата;

признак вспомогательного переноса AF, указывающий на перенос из третьего разряда или на заем в третий разряд результата при выполнении арифметических операций;

признак четности PF, указывающий иа четное число единиц в младшем байте результата;

признак переноса CF, указывающий иа перенос из старшего разряда или на заем в старший разряд результата.

В группу признаков управления входят:

признак направления DF, указывающий направление обработки строк данных;

признак разрешения прерывания IF, разрешающий или запрещающий максируемые прерывания;

признак пошагового режима TF, управляющий пошаговыми прерываниями. Распределение признаков по разрядам регистра признаков показано на рнс. 16.3.

Микропроцессор обеспечивает формирование 20-разрядного адреса для адресации ячейки внешней памяти. Память организована линейная последовательность в 1М байт с адресами от 00000Н до FFFFFH. Структурными единицами памяти являются: ячейка, слово, двойное слово и сегмент.

|

Рис 3 |

Таблица 3

Тип прерывания |

|

|

Время вы зова процедуры (в тактах) |

Прерывание по ошибке деления |

0 |

1 |

50 |

Пошаговое прерывание |

1 |

4 |

50 |

Немаскируемое прерывание |

2 |

2 |

50 |

Прерывание по точкам разрыва (по команде INT3) |

3 |

1 |

52 |

Прерывание по переполнению (по команде INTO) |

4 |

1 |

53 |

Прерывания, определяемые пользователем (по команде INTNPROC) |

5-31 |

1 |

51 |

Маскируемые прерывания |

32—255 |

3 |

61 |

Ячейка памяти — минимальная адресуемая единица памяти, используемая для запоминания 8-разрядных данных (байта данных).

Слово памяти — две последовательные ячейки памяти, которые используются для запоминания 16-разрядных данных (слова данных), причем младшие восемь разрядов всегда хранятся в ячейке памяти с меньшим адресом, а старшие — с большим. При адресации 16 разрядных данных указывается адрес первой ячейки слова памяти. Слово памяти может располагаться в памяти как по четному, так и нечетному адресу. Чтение (запись) данных из слова памяти по четному адресу осуществляется за одно обращение к памяти, а по нечетному — за два обращения.

Двойное слово памяти — четыре последовательные ячейки памяти или два последовательных слова памяти, которые используются для запоминания 32-разрядных данных. При адресации 32-разрядных данных указывается адрес первой ячейки двойного слова памяти. Двойное слово памяти также может иметь четный или нечетный адрес.

Для достижения максимальной производительности слова и двойные слова данных должны размещаться в памяти по четным адресам.

Программы, написанные для микропроцессора КМ1810ВМ86 «рассматривают» 1М байт памяти как группу сегментов, определяемых конкретным применением.

Сегмент памяти — участок памяти, емкость которого может изменяться от 16 до 65536 байт; начинается с адреса, кратного ЮН. Каждому сегменту соответствует непрерывная и отдельно адресуемая область памяти.

Сегменты могут следовать друг за другом непрерывно, с интервалом или могут перекрываться. Максимальное количество следующих непрерывно друг за другом сегментов емкостью 16 бант равно 65536, а емкостью 65536 байт равно 16. Программный сегмент может быть настроен на адрес любой ячейки сегмента, на адрес любого слова сегмента.

Микропроцессор позволяет независимо адресовать четыре программных сегмента в памяти, называемых текущими сегментами команд, данных, стека и текущим дополнительным сегментом.

Сегментирование памяти совместно с позицнонно-независимыми командами передачи управления позволяет создавать динамически перемещаемые программные модули.

Физически область памяти для

КМ1810ВМ86 организуется как два банка памяти по 512К байт: старший банк (D15—D8) и младший банк (D7—D0). Для адресации ячеек памяти в каждом банке используются разряды А19—А1 канала адреса микропроцессора. Байт данных с четным адресом пересылается по линиям D7—DOканала данных, а байт данных с нечетным адресом - по линиям D15—D8 канала данных. Микропроцессор вырабатывает сигналы ВНЕ и АО, используемые для выбора соответствующего банка памяти.

Младший банк, содержащий четно адресуемые байты, выбирается при А0 = 0. Старший банк, содержащий нечетно адресуемые байты, выбирается при ВЯ£ = 0.

Команды всегда выбираются из памяти Kah слова, независимо от четности или нечетности адреса, по которому производится чтение команды.

Микропроцессор позволяет обрабатывать 256 типов прерываний с номерами от 0 до 255, которые делятся на внешние аппаратные, внутренние аппаратные и программные. Запросы на внешние прерывания формируются внешними по отношению к микропроцессору устройствами. Запросы на внутренние прерывания формируются при выполнении определенных команд или по некоторым условиям при выполнении команд. По любому прерыванию управление передается программе (процедуре) обслуживания прерывания посредством вектора прерывания, выбираемого из таблицы векторов прерывания, располагаемой в памяти. Номер вектора прерывания и приоритет для всех типов прерывания приведены в табл. 16.5.

Запросы на внешние прерывания восприми маются и обрабатываются после выполнения текущей команды. Внешние прерывания поступают на микропроцессор по двум внешним выводам (INTн NMI) и делятся па маскируемые и немаскируемые.

Запросы на маскируемые прерывания от внешних устройств обычно поступают на входы контроллера прерываний КР1810ВН59А, который формирует сигнал запроса прерывания INTмаскируемого прерывания с наибольшим приоритетом. Обработка маскируемого прерывания зависит от значения признака разрешения прерывания IF. Управление признаком IFосуществляется командой СИ, запрещающей прерывания, и командой STI, разрешающей прерывания. Если прерывания разрешены и пришел запрос на маскируемое прерывание, то после его распознавания микропроцессор формирует сигнал подтверждения прерывания INTAдля контроллера прерываний. Контроллер прерываний в ответ на этот сигнал выдает байт данных, который определяет номер прерывания в пределах от О до 255.

Немаскируемый запрос прерывания поступает по входу NMIмикропроцессора и обычно используется для прерывания работы микропроцессора при «катастрофических» событиях, таких как пропадание питания, обнаружение ошибки памяти и т. д. Обработка немаскируемого прерывания не зависит от значения

признака IF, сигнал INTAне вырабатывается, а номер вектора прерывания формируется внутри микропроцессора.

Обработка внутренних прерываний не зависит от значения признака разрешения прерывания, и номер вектора прерывания формируется внутри микросхемы.

Внутренние аппаратные прерывания делятся на прерывание по ошибке деления и пошаговые прерывания.

Прерывание по ошибке деления происходит во время выполнения команд деления DIV, ID1V, если результат деления превышает максимально допустимую величину или в случае деления на нуль.

Выработка пошагового прерывания зависит от состояния признака пошагового режима TF. Если TF=\, то пошаговое прерывание генерируется после выполнения каждой текущей команды или пары текущих команд, первой из которых является команда изменения содержимого сегментного регистра. Пошаговые прерывания обычно используются в программах отладки.

Программные прерывания делятся на прерывания по точкам разрыва, прерывания, определяемые пользователем, и прерывания по переполнению. Обработка программных прерываний не зависит от значения признака разрешения прерывания.

Прерывание по точкам разрыва генерируется по однобайтовой команде INT3. Точка разрыва в общем случае представляет собой любое место в программе, где нормальное ее выполнение приостанавливается для выполнения некоторых специальных действий. Обычно данное прерывание используется в программных средствах отладки.

Прерывание по переполнению генерируется по однобайтовой команде INTOи зависит от значения признака переполнения OF. Если 0F=1, то по команде INTOвыполняется переход на процедуру обслуживания прерывания, если OF = 0, то прерывания ие происходит. Прерывание по переполнению может быть использовано для обнаружения переполнений прн выполнении операций иад целыми числами.

В случае прерываний, определяемых пользователем, номер прерывания задается вторым байтом кода команды INT. Данный вид прерывания может быть использован для вызова системных процедур и (или) процедур пользователя в любом месте программы.

Микропроцессор КМ1810ВМ86 допускает разработку на его основе мультипроцессорных систем, так как в нем заложена возможность синхронизации работы нескольких процессоров. В мультипроцессорных системах, выполненных на основе КМ1810ВМ86, возможно использование процессоров двух типов: независимых и подчиненных (сопроцессоров). Независимый процессор выполняет свой собственный поток команд. Сопроцессор отличается от независимого тем, что следит за выполнением потока команд центральным процессором, идентифицирует в этом потоке свои команды и выполняет их и таким образом расширяет набор команд центрального процессора.

Для обеспечения возможности разделения системного канала при работе нескольких процессоров К.М1810ВМ86 по команде LOCK вырабатывает сигнал блокировки канала LOCK, который запрещает другим процессорам пользоваться системным каналом на время выполнения команды, следующей за командой LOCK. Данная команда совместно с командой XCHGможет быть использована для координации доступа к совместно используемым ресурсам через «семафор» — программно-управляемый признак в памяти.

Микропроцессор КМ1810ВМ86 может быть синхронизирован по отношению к внешним событиям с помощью команды WAITи входного сигнала TEST.

В систему команд К.М1810ВМ86 входит

команда ESC(расширение), которая представляет другому процессору (сопроцессору) возможность получения команд и данных из программы, выполняемой микропроцессором.

Команда ESCсовместно с командой WAIT

используется для организации параллельных

процессов (программ) в мультипроцессорной

системе.

Отличительной особенностью КМ1810ВМ86 является возможность аппаратной перестройки внутренней структуры схемы управления и синхронизации. Выбор режима функционирования этой схемы предоставляет разработчику системы возможность выбора подмножества выходных управляющих сигналов в соответствии со степенью сложности проектируемой микропроцессорной системы. Системная «настройка» обеспечивается специальным выводом выбора режима MN/MX.

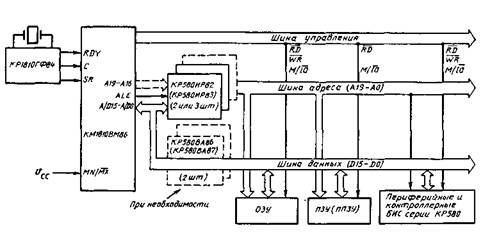

Минимальный режим (вывод MN/MXподключен к шине питания) ориентирован на применение микропроцессора в однопроцессорных системах, содержащих небольшое число устройств.

|

Рис 4 |

В этом режиме микропроцессор непосредственно вырабатывает^ сигналы управле ния циклами канала DT/R, DEN, ALE, M/IO, RD, WR, INTAв соответствующей временной последовательности, а также обеспечивает простой доступ к системному каналу по запросу от контроллера прямого доступа к памяти типа КР580ВТ57, используя сигналы HLD/HLDA

Система минимальной сложности, как по казано на рис. 16.4, состоит из К.М1810ВМ86, генератора тактовых импульсов КР1810ГФ84, двух (трех) буферных регистров КР580ИР82, обеспечивающих фиксацию 16-разрядного (20-разрядного) адреса. Подключение шины данных системы к выходам канала данных микропроцессора выполняется специальными схемами двунаправленных шинных формирователей КР580ВА86. Если нагрузка по току и емкостная нагрузка не превышают нагрузочной способности выходных каскадов микропроцессора, то возможно непосредственное подключение его канала данных На шину данных системы.

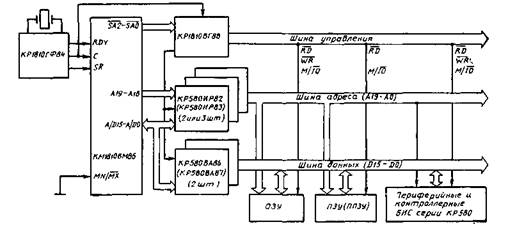

Максимальный режим (вывод MN/MXподключен к шине «Общий») ориентирован на применение микропроцессора в сложных однои многопроцессорных системах. В системах максимальной конфигурации (рис. 16.5) функции управления каналом берет на себя системный контроллер К.Р1810ВГ88, который декодирует трн сигнала состояния SAO—SA2, поступающие из микропроцессора, и расширенный набор сигналов управления для остальной части системы

|

Рис 5 |

Пять выходных сигналов используются для координации совместной работы с другими процессорами в мультипроцессорной системе.

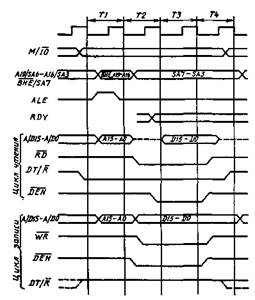

Для пользователя действия, выполняемые микропроцессором, представляют собой последовательность циклов канала по обмену информацией с памятью или периферийными устройствами. Каждый цикл канала микропроцессора состоит, как минимум, из четырех машинных тактов 77—74. В такте 77 на каиал адреса'данных всегда выдается адресная информация. В этом же такте вырабатывается сигнал ALE, который позволяет идентифицировать начало цикла канала и используется как стробирующий для занесения адресной информации во внешний регистр адреса.

В такте 72 производится переключение направления работы канала адреса/данных. Передача данных по каналу происходит в тактах 73 и 74. Длительность цикла канала может быть удлинена использованием управляющего сигнала RDY. Этот сигнал позволяет разработчику синхронизировать скорость работы внешней памяти со скоростью работы микропроцессора введением в цикл канала между тактами 73 н 74 дополнительных тактов ожидания TWI. В течение тактов ожидания данные на канале остаются неизменными. Между тактом Т4 текущего цикла и тактом 77 следующего цикла канала процессор может вводить дополнительные «холостые» такты, предназначенные для выполнения внутренних действий. Моменты введения этих тактов и их число зависят от состояния очереди команд и выполняемой команды в У О,

Все типы циклов канала могут быть объединены в два базовых цикла: цикл чтения и цикл записи. Пример базового цикла канала для минимального режима приведен на рис. 16.6.

Цикл чтения начинается с выработки сигнала ALE. Этот сигнал используется для занесения адресной информации на внешний регистр адреса. В такте Т2 канал A/Dпереключается в высокоомное состояние, вырабатывается сигнал RD, который используется для чтения адресуемого устройства. Для управления шинными формирователями, обеспечивающими развязку канала адреса/данных микропроцессора от системного канала данных, используются сигналы DT/Rи DEN.

Цикл записи (как и цикл чтения) начинается с выдачи сигнала ALEи адреса иа канал адреса. В такте 72 непосредственно за выдачей адреса на канал A/Dвыдаются данные для записи в адресуемое устройство. Эта информация остается истинной на канале данных до окончания такта 74 Сигнал WRвырабатывается в начале такта Т2 и остается в этом состоянии до начала такта 74.

Использование четырехтактового цикла обмена информацией позволяет микропроцессору при тактовой частоте 5 МГц работать без введения тактов ожидания со схемами памяти с длительностью цикла обращения от 500 до 800 не и временем выборки от 300 до 400 не.

Начальная установка и запуск микропроцессора осуществляются по сигналу SR.

|

Рис 6 |

Для правильной установки в начальное состояние микропроцессора сигнал SRдолжен подаваться на вход SRвысоким уровнем — не менее четырех периодов тактовой частоты. По сигналу SR работа микропроцессора приостанавливается, н производится начальная установка регистра признаков F, регистра адреса (указателя) команд IP, сегментных регистров в соответствии с табл. 16.6, выходы канала адреса/ данных переводятся в высокоомное состояние, выходы канала управления — в высокоомное или пассивное состояние.

По окончании сигнала SRпошаговые и маскируемые прерывания запрещены, и первая команда начинает выбираться из ячейки памяти с физическим адресом FFFFOH. Обычно первой командой является команда межсегментного прямого перехода IMP, которая изменяет содержимое регистров IPи CSи таким образом определяет начальный адрес выполняемой программы.

Таблица 4

Назначение регистра |

Содержимое регистра |

Регистр признаков F |

F00216 |

Регистр адреса команды IP |

000016 |

Регистр сегмента команд CS |

FFFF16 |

Регистр сегмента данных DS |

0000i6 |

Регистр сегмента стека 5S |

0000,6 |

Регистр дополнительного сегмента ES |

0000,6 |

Система команд микропроцессора содержит 135 машинных команд, которые могут быть разделены на шесть категорий: команды пересылки данных, арифметические команды, команды поразрядной обработки данных, строковые команды, команды передачи управления, команды управления микропроцессором. Команды пересылки данных предназначены для пересылки содержимого операнда-источника на место операнда-приемника. Существует четыре группы команд пересылки данных: общего назначения, ввода/вывода, логического адреса, признаков.

Арифметические команды предназначены для выполнения основных арифметических операций (сложение, вычитание, умножение и деление) над порядковыми и целыми двоичными числами, над упакованными и распакованными двоично-десятичными числами, а также для преобразования форматов данных.

Команды поразрядной обработки данных предназначены для выполнения логических операций и операций линейного и циклического сдвигов (арифметических и логических) на одни нли п разрядов.

Команды обработки элементов строк данных предназначены для пересылки, сравнения, записи в память, загрузки в аккумулятор элементов строк данных. Команды обработки строк совместно с префиксом повторения позволяют организовать аппаратные циклы для обработки элементов строк длиной до 64К байт.

Команды передачи управления предназначены для организации перехода в программе. Существует четыре класса таких команд: безусловная передача управления, условная передача управления, управление циклами, команды прерываний.

Команды управления микропроцессором позволяют программно управлять его различными функциями н делятся на две группы-команды управления состоянием признаков, команды синхронизации работы микропроцессора с внешними событиями.

Система команд КМ1810ВМ86, упорядоченных по коду операции, приведена в табл 16.7, установка признаков состояния прн выполнении команд — в табл. 16.8, набор машинных команд, упорядоченных по мнемокоду, показан в табл. 16.9.

Команды микропроцессора обеспечивают выполнение операций над одним или двумя операндами, и результат операции может записываться по адресу любого из операндов. В зависимости от типа команды операнды могут быть расположены в программно-доступных регистрах, непосредственно в коде команды, в памяти и регистрах ввода/вывода. Непосредственные данные могут быть типа байта или слова. Операнды в программно-доступных регистрах могут быть типа байта или слова, а для команд умножения и деления — типа двойного слова.

Операнды в памяти могут быть типа байта, слова, двойного слова, а в регистрах ввода/вывода — типа байта и слова.

Для указания операнда в программно доступных регистрах используются регистровая и неявная регистровая адресации. При регистровой адресации номер 8- или 16-разрядного регистра, содержащего операнд, указывается в поле REGкода команды. При регистровой неявной адресации номер регистра определяется неявно самим кодом команды.

Для указания операнда в коде команды используется непосредственная адресация.

Для указания операндов в памяти используется прямая, косвенная регистровая, стековая, строковая и табличная адресации. Адрес операнда в памяти состоит из двух 16-разрядных компонент: базы сегмента и смещения относительно базы сегмента, называемого исполнительным адресом (ЕА).

База сегмента хранится в сегментном регистре. Исполнительный адрес представляет собой расстояние в байтах от начала сегмента, содержащего операнд, до операнда и интерпретируется как порядковое число от 0 до 65535. Составными частями, используемыми при вычислении исполнительного адреса операнда, являются: смещение в команде (DISP8/16), содержимое базового регистра ВХ или ВР, содержимое индексного регистра 5/ или DI. Способ и время вычисления исполнительного адреса определяются полями MODи RIMкода комацды и приведены в табл 16 10.

При прямой адресации исполнительным адресом операнда является смещение в команде.

При косвенной регистровой адресации в коде команды задается способ вычисления исполнительного адреса операнда. Имеются четыре типа косвенной регистровой адресации'

через содержимое базового или индексного регистра ВХ, ВР, SI, DI;

через сумму содержимого базового нли индексного регистра BP'BXiSI'Dlи смещение и команде;

через сумму содержимого базового ВР'ВХ и индексного SIJD! регистров;

через сумму содержимого базового ВР ВХ н индексного SVDIрегистров и смещения в команде.

При стековой адресации исполнительный адрес операнда находится в регистре указателя стека SP, причем после чтения операнда нз стека содержимое регистра указателя стека увеличивается на два, а перед записью операнда в стек содержимое регистра указателя стека уменьшается на два.

При строковой адресации исполнительный адрес операнда находится в регистре индекса источника 5/ и (нли) регистре индекса приемника DI.

После обращения к операнду содержимое указанного регистра увеличивается илн уменьшается в зависимости от значения признака направления DF. Данный вид адресации ис |