Подсистема прямого доступа в память МПС

Рассмотрим вариант программно-управляемого обмена между памятью и внешним устройством в МПС на базе МП i8080. Пусть необходимо передать массив данных длиной L, начиная с адреса ADR на ВУ с адресом AIO. Положим, что начальный адрес массива загружен в регистровую пару HL, а длина массива - в регистр C. Тогда фрагмент программы обмена может иметь следующий вид:

Табл. 6.1

Метка |

Мнемокод |

Комментарий |

Количество

машинных циклов |

LM: |

MOV A,M |

Чтение байта в Акк. |

2 |

|

OUT AIO |

Выдача байта на ВУ |

3 |

|

INX H |

Модификация адреса |

1 |

|

DCR C |

Модификация счетчика |

1 |

|

JNZ LM |

Переход, если массив не исчерпан |

3 |

|

|

Всего: 10 |

Таким образом, для того, чтобы в рамках процедуры копирования массива данных из памяти в ВУ переслать один байт данных потребуется десять машинных циклов (МЦ). Процессоры с более совершенной системой команд могут использовать для этой цели меньшее число МЦ, но все равно их будет более одного.

Управляя обменом, микропроцессор "ведет" два счетчика - адресов массива и количества переданных байт и формирует сигналы управления на магистраль. Если снабдить ВУ аппаратными счетчиками и схемой формирования управляющих сигналов (т.н. "канал прямого доступа в память"), то передачу одного байта (слова) можно осуществить за один МЦ без участия процессора. Необходимо лишь на время передачи данных под управлением канала ПДП блокировать работу процессора, отключив его от системной шины. Для этого служит вход захвата шины HOLD. Если подать на него высокий уровень, то МП по окончанию текущего МЦ безусловно перейдет в режим ожидания, переведя все свои выходные линии, кроме HLDA и WAIT, в высокоимпедансное состояние, а выходы HLDA и WAIT - в состояние лог. "1". Выходной сигнал HLDA используется для отключения МП от системной шины - перевода шинных формирователей, включенных между локальной и системной шиной, в высокоимпедансное состояние.

Если в МПС используется несколько ВУ, снабженных каналом ПДП, то целесообразно использовать специальный контроллер ПДП, который обеспечивает программирование каналов ПДП, подключение их к системной шине и дисциплину обслуживания.

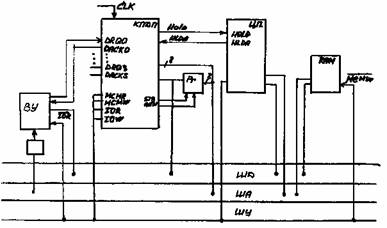

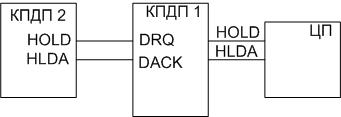

Рис. 6.1. Типовое включение КПДП в МПС

Контроллер прямого доступа в память К580ВТ57

Микросхема К580ВТ57 предназначена для управления передачей информации между ВУ о ЗУ в режиме ПДП. Основное назначение контроллера - формирование последовательности адресов и управляющих сигналов.

Контроллер ПДП имеет четыре независимых канала обмена. Блок управления каждого канала включает два 16-разрядных регистра : регистр начального адреса РА и регистр управления РУ, причем РУ[13:0] хранит длину передаваемого массива (количество передаваемых байт), а РУ[15:14] - режим работы канала. Структурная схема контроллера и схема подключения его к МПС показана на Ошибка! Источник ссылки не найден.2.

Рис. 6.2. Контроллер прямого доступа в память

Контроллер включает в себя, помимо четырех каналов ПДП, схему управления, обеспечивающую связь с системной шиной, разрешение конфликтных ситуаций в соответствии с заданной системой приоритетов и управление работой контроллера в различных режимах.

Схема управления содержит два восьмиразрядных регистра, общие для всех каналов - регистр режимов РгР и регистр состояний РгС, причем РгР доступен процессору только по записи, а РгС только по чтению. Форматы регистров РгР и РгС показаны на Рис. 6.3.

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

Рг Р : |

AL |

TCS |

EW |

RP |

EN3 |

EN2 |

EN1 |

EN0 |

Рг С : |

0 |

0 |

0 |

UF |

TC3 |

TC2 |

TC1 |

TC0 |

Рис. 6.3. Форматы регистров режима и состояния

В регистре режимов разряды имеют следующий смысл:

- AL - автозагрузка;

- TCS - отключение канала;

- EW - расширенная запись;

- RP - циклический приоритет;

- EN[3:0] - разрешение работы каналов 3..0.

В регистре состояния:

- UF - флаг обновления;

- TC[3:0] - конец счета в каналах 3..0.

Выводы контроллера можно разделить на две группы : (а) линии связи с ВУ и (б) линии связи с системной шиной МПС.

а)

DRQ[0:3] - запросы от ВУ (каналов) на прямой доступ в ЗУ;

DACK[0:3]\ - разрешения на ПДП внешним устройствам;

TC - конец счета, сигнал H-уровня на этом выходе отмечает последний цикл передачи блока данных;

MARK - маркер - сигнал H-уровня указывает, что до конца передаваемого блока необходимо выполнить число циклов обмена, кратное 128.

б) Линии связи с системной шиной передают стандартные сигналы управления, которые используются традиционно : RESET, READY (контроллер анализирует состояние готовности и при необходимости, как и МП, вставляет такты ожидания Tw), RDM\, WRM\, RDIO\, WRIO\, HRQ, HLDA. Контроллер синхронизируется внешним системным синхросигналом, в качестве которого чаще всего используется Ф2ттл. Сигнал ADSTB не поступает на системную шину и служит для "защелкивания" старшего байта адреса, передаваемого по шине данных в режиме ПДП (см. ниже). Сигнал AEN отмечает время действия цикла ПДП и может быть использован в системе для предотвращения захвата шины другими устройствами. Вход CS\ обеспечивает выбор микросхемы при адресной селекции.

Перед началом работы контроллера по сигналу RESET очищаются регистры всех каналов и регистр режимов РгР. Очистка РгР приводит к запрету работы всех каналов во всех режимах и предотвращает конфликты на шинах при подаче напряжения питания. Разрешение работы каналов не должны включаться, пока в регистры адресов и управления соответствующих каналов не будут загружены необходимые числа. В противном случае запрос DRQ от ВУ может вызвать циклы ПДП и порчу данных в памяти.

Контроллер ПДП может работать в двух режимах : в режиме программирования и в режиме ПДП.

В режиме программирования контроллер является пассивным устройством и процессор осуществляет с ним связь как с обычным ВУ. При этом линии A[3:0] и RDIO\, WRIO\ являются входными. Линии адреса A[2:1] при A[3] = 0 используются для селекции канала (код соответствует номеру канала), а тип регистра в канале идентифицируется разрядом A[0]: "0" - РгA, "1" - РгУ. Поскольку РгА и РгУ - двухбайтовые регистры, их загрузка осуществляется двумя циклами записи по одному адресу, причем в первом цикле передается младший байт.

При A[3:0] = 1000 осуществляется запись в РгР или чтение из РгС.

Разряды 0..3 регистра режимов РгР разрешают или запрещают работу соответствующих каналов ("1" - разрешено, "0" - запрещено).

Разряд РгР[4] устанавливает тип приоритета работы каналов. При РгР[4] = 0 установлен фиксированный приоритет (канал 0 -высший, канал 3 - низший). При РгР[4] = 1 устанавливается циклический приоритет каналов. В этом режиме после каждого цикла ПДП (но не запроса) приоритет каждого канала изменяется. Канал, который только что был обслужен, получает низший приоритет, а остальные каналы - по кольцу 0 - 1 - 2 - 3 - 0 -.

Циклический сдвиг приоритетов предотвращает монополизацию одного канала; последовательность циклов ПДП будет обслуживать различные каналы, если их работа не запрещена. Все операции начинаются с присвоения каналу 0 высшего приоритета.

Разряд РгР[5] = 1 определяет режим опережающей записи. В этом случае длительность сигналов WRM\ и WRIO\ увеличивается за счет более ранней их активизации в цикле ПДП. Это в некоторых случаях позволяет обойтись без тактов ожидания Tw.

Состояние "1" в разряде РгР[6] определяет режим автоматического отключения канала по сигналу TC. Этот сигнал возникает когда РгУi[13:0] = 0; в этом случае сбрасывается бит разрешения работы активного канала и запустить его вновь в работу можно только путем программной перезагрузки РгР. При РгР[6] = 0 появление TC не запрещает дальнейшую работу канала.

При наличии "1" в РгР[7] устанавливается режим автозагрузки, позволяющий каналу 2 многократно передавать массив данных без программного вмешательства. При программировании канала 2 в этом режиме его параметры (РгА и РгУ) автоматически дублируются в соответствующих регистрах канала 3 и по сигналу TC переписываются из канала 3 в канал 2, восстанавливая первоначальное значение РгА2 и РгУ2, причем эта передача сопровождается установкой флага обновления UF в РгС[4]. Заметим, что возможности режима TCS (отключение каналов) не распространяются на канал 2 в режиме автозагрузки.

Если не запретить работу канала 3 в режиме автозагрузки, то он может работать как обычно при отсутствии запроса DRQ2. Однако, следует помнить, что работа канала 3 изменит значения параметров, которые должны передаваться в канал 2.

Перед началом работы каждый канал программируется путем занесение в РгА начального адреса массива, в РгУ[13:0] - количества передаваемых байт, а в РгУ[15:14] - режима работы канала (00 контроль, 01 - запись в ЗУ, 10 - чтение из ЗУ).

Режим контроля может использоваться ВУ для контроля принятых данных, т.к. в этом режиме не производится передача данных (не вырабатываются сигналы RDM\, RDIO\, WRM\, WRIO\), а все остальные функции ПДП сохраняются.

В режим ПДП контроллер переходит при поступлении запроса DRQ незамаскированного канала. Он вырабатывает запрос микропроцессору HRQ на захват шины и, получив подтверждение HLDA, передает сигнал активизации DACK\ выбранному ВУ и начинает циклы ПДП.

В цикле ПДП контроллер выдает содержимое РгА на линии A[7:0] (младший байт) и линии D[7:0] (старший байт в сопровождении строба ADSTB) и, в зависимости от режима работы канала, одну из пар управляющих сигналов RDM\ + WRIO\ или RDIO\ + WRM\ (в режиме контроля управляющие сигналы не выдаются). Режим ПДП завершается при снятии сигнала DRQ.

Каскадирование КПДП

Рис. 6.4. Каскадирование КПДП

Организация ПДП в IBM PC

В современных машинах используются дополнительные контроллеры ПДП, один из которых 16-ти разрядный, но также есть и 8-ми разрядные.

При программировании контроллера указываются адреса, приоритеты, регистр страниц ПДП.

Рис. 6.5. Организация ПДП в IBM PC

Высокопроизводительный 32-разрядный контроллер ПДП 82380

Контроллер 82380 выполнен в 132-выводном корпусе типа PGA и представляет собой высокопроизводительное 32-разрядное устройство, обеспечивающее прямой доступ к памяти и спроектированное специально для использования в системах на базе микропроцессора 80386. Контроллер 82380 является первым коммерческим устройством, в котором реализованы функции управления ПДП по восьми независимым программируемым каналам. Контроллер 82380 повышает общую пропускную способность шины микропроцессора 80386. Применение 32-разрядного интерфейса контроллера обеспечивает эффективную передачу данных и повышает скорость обслуживания системных устройств ввода-вывода в 5 — 10 раз по сравнению с известными схемотехническими решениями. Эти особенности наиболее важны в системах, требующих быстродействующей компьютерной техники, таких как многозадачные учрежденческие рабочие станции, промышленная связь и автоматизация, САПР, гибкие производственные системы и системы искусственного интеллекта. Специализированная ориентация контроллера 82380 на особенности интерфейса микропроцессора 80386 предельно минимизирует объем соответствующих логических схем.

Контроллер 82380 называют также интегрированным системным периферийным устройством, поскольку он выполняет ряд типовых для вычислительных систем функций, обычно реализуемых на отдельных компонентах БИС и СБИС. В состав таких средств входят

- логические схемы системного сброса;

- 20-уровневый программируемый контроллер прерываний (функциональное расширение программируемого контроллера прерываний 82С59А фирмы Intel);

- четыре 16-разрядных программируемых таймера;

- программируемый генератор с состояниями ожидания;

- контроллер регенерации динамического ОЗУ;

- схемы управления и арбитража внутренней шины.

Структурная схема контроллера 82380 показана на Рис. 6. . Для каждого из восьми независимых каналов передачи данных в контроллере 82380 имеется вспомогательная регистровая память, поддерживающая обмен данными произвольной разрядности. Это позволяет исключить дополнительные внешние цепи для. выполнения действий по выравниванию данных на определенную границу. В результате контроллер обеспечивает передачу данных между устройствами с разными размерами тракта данных по одному каналу.

Архитектура контроллера 82380

Рассмотрим основные, вопросы сопряжения контроллера 82380 с микропроцессором 80386 через локальную шину. Далее будет описан ряд функций, реализованных в кристалле 82380, для выполнения которых в обычных условиях требуется 20 – 30 соответствующих БИС и СБИС. Для обеспечения совместимости с существующими программными продуктами в структуре контроллера 82380 имеются побайтно доступные регистры. Если внутренним логическим схемам контроллера 82380 требуется некоторая задержка до того момента, как кристалл станет доступен микропроцессору 80386, то контроллер автоматически вставит в цикл обращения необходимые такты ожидания; при этом программисту не нужно беспокоиться об этих временных аппаратных особенностях. В структуре контроллера ПДП нашли отражение как программные, так и аппаратные решения вопросов по сбросу микропроцессора 80386, а также по управлению микропроцессором, находящимся в состоянии останова.

Контроллер 82380 может работать как в режиме ведущего устройства, так и в подчиненном режиме. Поскольку после системного сброса контроллер ПДП переходит в подчиненный режим, то для системы он представляется как устройство ввода-вывода. В подчиненном режиме контроллер 82380 отслеживает состояние микропроцессора 80386 и отрабатывает каждую команду в установленном порядке. Выполняя функцию управления ПДП, контроллер следит за состоянием потока адресов для устройства, к которому происходит обращение, и добавляет необходимое число тактов ожидания в цикл обращения. При выполнении операций передачи с ПДП контроллер работает в привилегированном режиме как ведущее устройство на шине.

Интерфейс с главным процессором

Контроллер 82380 подключен непосредственно к локальной шине микропроцессора 80386, поэтому назначение его управляющих сигналов такое же, как у 80386. Контроллер 82380 отслеживает текущее состояние микропроцессора 80386 как по его сигналам состояния, так и по сигналам на своих выводах ADS* и READY*. На основании этой информации контроллер определяет, выполняются конвейерные или неконвейерные действия в текущем цикле шины.

Рис. 6.6. Архитектура контроллера 82380

Контроллер 82380 может управлять доступом к 8-разрядным периферийным устройствам с целью обеспечения совместимости с существующими архитектурами систем и программными продуктами. При этом данные размещаются на линиях шины D0 — D7 или D8 — D15. В подчиненном режиме контроллер только принимает данные по указанным линиям. Благодаря возможности контроллера 82380 обращаться к байтам программист может иметь доступ к регистрам контроллера, пользуясь при этом холостыми командами NOP для организации ожидания срабатывания менее быстродействующих внутренних регистров 82380. В подчиненном режиме 82380 контролирует линии состояния и управления центрального процессора, отрабатывая логику шины микропроцессора 80386 и добавляя требуемое число тактов ожидания.

В режиме ведущего работа контроллера 82380 полностью согласуется с работой микропроцессора 80386. Например, данные передаются и принимаются контроллером точно так же, как микропроцессором 80386. Для остальной части системы и любого подключенного периферийного устройства контроллер 82380 выглядит как микропроцессор 80386. Это значит, что при разработке систем на базе данного контроллера нет необходимости видоизменять интерфейс с уже существующими периферийными устройствами. Механизм обращения контроллера 82380 к любому периферийному устройству на шине остается таким же, как у микропроцессора 80386; дополнительно контроллер выявляет конвейерные циклы шины.

Адреса всех регистров данных, управления и состояния контроллера 82380 фиксированы относительно друг друга. Эти регистры могут быть отображены на соответствующие ячейки либо оперативной памяти, либо пространства ввода-вывода.

Функции контроллера ПДП

На Рис. 6.7 показана структура 32-разрядного восьмиканального контроллера ПДП в составе кристалла 82380. При проектировании контроллера ставилась задача эффективной передачи произвольных комбинаций байтов, слов и двойных слов. С помощью контроллера ПДП можно адресовать полное пространство, покрываемое 32-разрядными физическими адресами, а также увеличивать и уменьшать адреса как операндов-источников, так и операндов назначения.

Рис. 6.7. Контроллер ПДП в 82386

С помощью внутреннего вспомогательного 32-разрядного регистра можно выполнять разборку и сборку данных разной разрядности, а также организовывать обмен данными между устройствами, имеющими разную ширину тракта данных. При работе контроллера 82380 на частоте 20 МГц и при передаче данных одинаковой разрядности может быть достигнута скорость обмена между памятью и устройствами ввода-вывода 25,6 Мбайт/с.

В порядке обслуживания как программных, так и аппаратных запросов ПДП контроллер может поддерживать обмен данными следующих типов:

- порт ввода-вывода — порт ввода-вывода;

- память — память;

- порт ввода-вывода — память;

- память — порт ввода-вывода.

Семь из восьми каналов (все, за исключением канала 4) имеют доступ к аппаратным сигналам подтверждения ПДП через трехразрядную шину подтверждения ПДП (линии от EDACK0 до EDACK2).

Каждый из восьми каналов контроллера ПДП 82380 функционирует независимо один от другого и может быть запрограммирован для работы в любом из допустимых режимов. Регистры каждого канала можно разделить на три класса: регистры счетчика байтов, регистры инициатора запроса и. целевые регистры; всего в канале имеется 24 регистра состояний и команд. С помощью этих регистров определяются адреса и объем пересылаемых данных. Регистр счетчика байтов (24 разряда) содержит значение числа байтов, которые должны быть переданы. Регистр инициатора запроса (32 разряда) содержит адрес порта ввода-вывода или памяти, где находятся данные, по которым был сделан запрос контроллеру на обслуживание ПДП; целевой регистр (32 разряда) содержит адрес порта ввода-вывода или памяти, по которому будут пересылаться данные.

Для каждого канала программист может выбирать дисциплину обслуживания с циклическими или фиксированными приоритетами. Циклический приоритет предусматривает разделение шины среди нескольких периферийных устройств, тогда как дисциплина с фиксированными приоритетами основана на определенных фиксированных параметрах, связанных с аппаратными и другими особенностями. В дисциплине с фиксированными приоритетами допускается, чтобы программист присваивал любому каналу низший приоритет, что позволит без перепрограммирования командных регистров изменять или приводить в исходное состояние расписание обслуживания приоритетов.

Каналы контроллера ПДП разделены на две группы по четыре канала — нижнюю и верхнюю. Нижние (от нулевого до третьего) и верхние (от четвертого до седьмого) каналы работают так, будто два отдельных контроллера ПДП включены по каскадной схеме. Такая организация работы позволяет одной группе присваивать фиксированные приоритеты, а другой — циклические, причем в различных комбинациях. По умолчанию каналы контроллера ПДП 82380 имеют фиксированные приоритеты, при этом высшим приоритетом обладает нулевой канал, низшим — седьмой. Нижняя группа играет своеобразную роль канала 5 в верхней группе и по порядку приоритетов располагается между каналами 7 и 4.

Как уже отмечалось, программисту предоставлена возможность по своему усмотрению выбирать, какому из каналов назначить низший приоритет. С помощью специальных команд определяется канал с самым низким приоритетом в пределах какой-либо группы, при этом остальным каналам присваиваются фиксированные приоритеты в последовательном порядке. Например, если низший приоритет присвоен каналу 1 в нижней группе, то порядок каналов по приоритетам будет следующий: 2 (высший приоритет), 3, 0, 1 (низший приоритет). Как видно, каналу, порядковый номер которого следует сразу же за номером выбранного канала с низшим приоритетом (в данном случае за номером 2), устанавливается самый высокий приоритет и так далее с убыванием приоритета по мере последовательного циклического в рамках группы возрастания номеров каналов, пока не будет достигнут номер выбранного наименее приоритетного канала (в данном случае номер 1). То же относится и к верхней группе каналов. Так, если низший приоритет присвоен каналу 6, то приоритеты верхней группы составят следующий ряд: 7 (высший приоритет), 4—6 (низший приоритет). Еще раз напоминаем, что нижняя группа по приоритету располагается между каналами 4 и 7. Поэтому по данным рассмотренных выше примеров комбинация двух групп даст следующий порядок каналов: 7 (высший приоритет), [2, 3, 0, I], 4, 5, 6 (низший приоритет).

Контроллер ПДП может принимать команды программного управления приоритетами только тогда, когда группа каналов, к которой относятся эти команды, находится в режиме с фиксированными приоритетами. При переходе к дисциплине с циклическими приоритетами все текущие уровни приоритетов остаются без изменений. При возврате от дисциплины с циклическими приоритетами к дисциплине с фиксированными приоритетами для уровней приоритетов каналов с помощью команд программного управления приоритетами восстанавливаются те значения, которые были в последний раз установлены программным образом.

Для дисциплины с циклическими приоритетами любой канал после обслуживания его запроса не остается с высшим приоритетом. Этому каналу присваивается низший приоритет. Следует помнить, что номера приоритетов нижней группы (в предыдущем примере 2, 3, 0, 1) меняются циклически в пределах верхней группы приоритетов (в предыдущем примере 7, [нижняя группа], 4 – 6). Поэтому обслуживание канала из нижней группы сопровождается циклическим изменением номеров уровня приоритета как в нижней, так и в верхней группах.

Такие команды, как "сброс запроса прерывания по завершении счета", "сброс режима ведущего устройства", "очистка регистра маски" и "сброс триггера указателя байтов", активизируются в результате распознавания контроллером ПДП 82380 соответствующего адреса порта. При этом в выбранный порт должны быть записаны какие-нибудь данные.

Контроллер ПДП 82380 реализует передачу блоков данных в одном из следующих режимов: режим одиночного буфера, буферный режим с автоинициализацией и режим с цепочкой буферов. Первый режим используется обычно в тех случаях, когда к моменту начала передачи известны объем и местоположение передаваемых данных, а данные размещены в непрерывной области памяти. Для данного режима характерно, что по завершении передачи одиночного блока контроллер ПДП должен перепрограммироваться для других передач даже этого же блока. В буферном режиме с автоинициализацией, напротив, допускается неоднократная передача контроллером ПДП одного и того же блока данных без перепрограммирования канала всякий раз.

В режиме с цепочкой буферов допускается, чтобы в программе был определен список буферов, содержимое которых передается, при этом для перепрограммирования контроллера ПДП используются программы обработки прерываний. Канал для передачи содержимого нового буфера программируется до того, как закончится передача содержимого текущего буфера. В данном режиме контроллер ПДП может работать с разрывными областями памяти и передавать все данные из этих областей за один рабочий процесс ПДП.

Программируемый контроллер прерываний

Рассмотрение функций контроллера 82380 продолжим с помощью Рис. 6.8. Функционально программируемый контроллер прерываний идентичен своим предшествующим моделям 8259А и 82С59А, за исключением программирования векторов прерываний. В контроллере 82380 объединены ресурсы трех контроллеров типа 82(С)59А. Каскадируя пятнадцать входов запросов прерываний контроллеров 82С59А, имеющихся в распоряжении программиста, можно организовать до 120 каналов запросов внешних прерываний. Хотя контроллеры могут работать в режиме ведущего устройства, приоритет отдается каскадному режиму.

В контроллере прерываний 82380 имеются более широкие возможности по использованию механизма векторов прерываний, поскольку каждый вход запроса прерываний может отдельно программироваться. Это значит, что каждому запросу прерываний может быть предписан свой собственный вектор прерывания; кроме того, системные программы по умолчанию могут присвоить контроллеру прерываний 82380 определенный вектор. Этот вектор используется в цикле подтверждения незапрашиваемых прерываний или прерываний, вызванных ошибочным запросом, с целью предупреждения системы о ложных прерываниях. С помощью прерывания система также информируется о том, что предпринята попытка запрограммировать векторы контроллера 82380 по методу контроллера 82С59А. Эта особенность гарантирует совместимость существующих программных продуктов с программным обеспечением, написанным для 82380. К другим усовершенствованиям контроллера прерываний 82380 относится возможность каскадного подключения внешних контроллеров прерываний, а также то, что квитирование установления связи между ведущим и ведомым устройствами вынесено из специализированных каскадных линий на шину данных.

На рис. 11.3 показаны пять основных блоков контроллера прерываний:

- регистр запросов прерываний (IRR);

- блок разрешения приоритетов (PR);

- служебный регистр (ISR);

- регистр маски (IMR);

- регистр векторов (VR).

Рис. 6.8. Структурная схема контроллера прерываний

Всеми прерываниями управляют каскадно включенные регистры запроса прерываний IRR и служебный регистр ISR. В регистре IRR фиксируются уровни всех прерываний, требующих обработки, а в регистре ISR — уровни всех прерываний, проходящих обработку. Во время цикла подтверждения прерывания с помощью блока разрешения приоритетов определяются приоритеты запросов по содержимому регистра IRR, а для прерываний с высшим приоритетом в регистре ISR помечаются соответствующие разряды. Регистр маски прерываний IMR используется совместно с регистром IRR и хранит код, по которому будут маскироваться определенные линии прерываний. Маскирование входов с более высоким приоритетом не влияет на линии запросов прерываний с низшим приоритетом. Номера предварительно запрограммированных векторов прерываний записываются в набор векторных регистров VR, для каждой линии запроса прерывания определен свой векторный регистр. Во время цикла подтверждения прерывания контроллера 82380 номер вектора, соответствующий выбранному прерыванию, выставляется на шину данных. |