1. Микросхема К589ИК02

Микросхема К589ИК02 - центральный процессорный элемент (ЦПЭ), представляет собой 2-разрядную микропроцессорную секцию, которая:

выполняет арифметические операции в двоичном дополнительном коде;

выполняет логические функции И, ИЛИ, НЕ и исключающее ИЛИ;

выполняет положительное и отрицательное приращения;

выполняет сдвиг влево и вправо;

выполняет проверку слова, части слова или одного разряда иа 0;

вырабатывает сигналы ускоренного переноса;

обладает возможностью наращивания разрядности;

имеет три типа шин входных данных, два типа шин выходных данных с тремя устойчивыми состояниями;

имеет 40 типов микрокоманд.

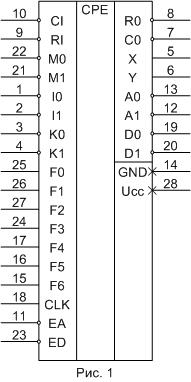

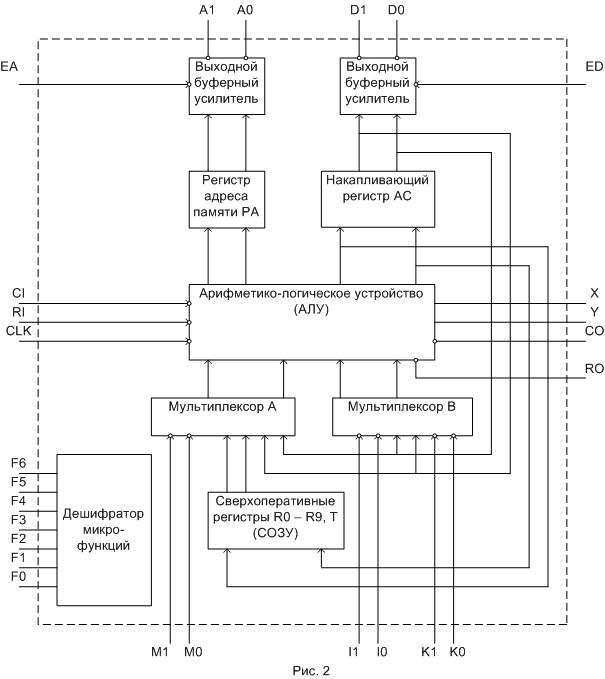

Микросхема содержит 11 регистров общего назначения и один накопительный регистр, независимый регистр адреса ЗУ, однотактную схему синхронизации. Условное графическое обозначение микросхемы приведено на рис. 1, назначение выводов — в табл. 1, структурная схема показана на рис. 2.

Таблица 1

|

| Вывод |

Обозначение |

Тип вывода |

Функциональное

назначение выводов |

| 1, 2 |

I0, I1 |

Входы |

Внешняя шина |

| 3, 4 |

K0, K1 |

Входы |

Маскирующая шина |

| 5, 6 |

X, Y |

Выходы |

Ускоренный перенос |

| 7 |

C0 |

Выход |

Перенос |

| 8 |

R0 |

Выход |

Сдвиг вправо |

| 9 |

R1 |

Вход |

Сдвиг вправо |

| 10 |

C1 |

Вход |

Перенос |

| 11 |

EA |

Вход |

Разрешение адреса |

| 12, 13 |

A1, A0 |

Выход |

Адрес памяти |

| 14 |

GND |

- |

Общий |

| 15-17 |

F6 - F5 |

Входы |

Коды микрокоманд |

| 24 - 27 |

F3, F0 - F2 |

|

|

| 18 |

CLK |

Вход |

Синхронизация |

| 19, 20 |

D0, D1 |

Входы |

Информация |

| 21, 22 |

M1, M0 |

Входы |

Информация |

| 23 |

ED |

Вход |

Разрешение данных |

| 28 |

Ucc |

- |

Напряжение питания |

|

Микросхема выполняет арифметические, логические, регистровые функции 2-разрядного микропрограммируемого центрального процессора. Данные от внешних источников (таких, как главная память, внешние устройства и т. п.) поступают в ЦПЭ по одной из трех входных шин. Данные от ЦПЭ передаются на внешние устройства по одной из двух выходных шин. Внутри ЦПЭ данные хранятся в одном из 11 регистров сверхоперативного ЗУ (СОЗУ) или в аккумуляторе. Данные от входных шин. из регистров и аккумулятора поступают в арифметико-логическое устройство (АЛУ) через два внутренних мультиплексора А и В. Дополнительные входы и выходы служат для обеспечения распространения переноса, сдвигов и выбора микрокоманды.

Семь линий входной шины микрокоманд (F0-F6) декодируются внутри ЦПЭ для выборки функций АЛУ, выработки адреса СОЗУ и управления мультиплексорами А и В.

Входная шина М предназначена для передачи данных из внешней главной памяти в ЦПЭ. Данные с шины М поступают через внутренний мультиплексор на вход АЛУ. Входная шина I предназначена для передачи данных от внешних систем ввода/вывода в ЦПЭ. Данные с шины I поступают также на вход АЛУ через мультиплексор, но независимо от шины М. Разделение на две шины обеспечивает относительно малую загрузку шин памяти даже в том случае, если к шине I подключено большое число устройств ввода/вывода.

При другом варианте использования шины входы I могут быть соединены внешним монтажом с одной из выходных шин для получения операции сдвига на несколько разрядов (например, на байт). В этом случае устройства ввода/вывода коммутируются внешними схемами на входы М.

Сверхоперативное ЗУ содержит 11 регистров (R0—R9 и Т). Данные с выхода СОЗУ поступают через внутренний мультиплексор на вход АЛУ, а с выхода АЛУ, в свою очередь, на вход СОЗУ.

Для запоминания результата операции АЛУ в ЦПЭ имеется независимый регистр АС — аккумулятор. Выход аккумулятора связан через внутренний мультиплексор со входом АЛУ; кроме того, выход аккумулятора подключен к выходному буферному каскаду (на три состояния) для выдачи иа выходную шину D. Обычно шина Dиспользуется для передачи данных во внешнюю главную память или внешние устройства ввода/вывода.

Мультиплексоры А и В выбирают данные для двух входов АЛУ в зависимости от данных на шине микрокоманд. На входы мультиплексора А подаются данные шины М, выход СОЗУ и аккумулятор, на входы мультиплексора В — данные шины I, аккумулятор и данные шины К. Данные на выбранном входе мультиплексора В всегда логически умножаются на содержимое соответствующего входа К для обеспечения гибкого маскирования и возможности проверки разрядов.

Арифметико-логическое устройство способно выполнять арифметические и логические операции, включая двоичное сложение в дополнительном коде, прибавление и вычитание, поразрядное логическое сложение и умножение, поразрядное исключающее ИЛИ—НЕ и М< поразрядное логическое дополнение. Результат операции АЛУ может быть записан в аккумулятор или в один из регистров СОЗУ. Для выполнения операции сдвига вправо выведены отдельные шины «Вход сдвига вправо» (RI) и «Выход сдвига вправо» (RO). Линии входа и выхода переноса (С/ и СО) предназначены для обеспечения нормального распространения последовательного переноса Данные на выходы СО и RO поступают через два буферных усилителя (на три состояния каждый), причем разрешается выдача либо только иа СО, либо только на RO. Кроме того, стандартные выходы для схем ускоренного переноса Xи У позволяют получить ускоренный перенос для произвольной длины слова.

Возможность маскировать входы АЛУ при помощи шины К значительно увеличивает универсальность АЛУ. При неарифметических операциях схемы переноса используются для получения логической сборки ИЛИ всех разрядов слова с целью анализа на 0 результата операции или одного из регистров (например, микрокоманды ANR, ORR).

Таким образом, ЦПЭ обеспечивает гибкую проверку содержимого разрядов. Шина К используется также при арифметических операциях для маскирования частей обрабатываемых полей. Дополнительной функцией шины К является передача констант из микропрограмм в ЦПЭ.

Состояния на выходах Xн Yформируются в соответствии со следующим правилом: если обозначить информацию, поступающую иа вход АЛУ с мультиплексора А, как at, aO, а с мультиплексора В как b1 и b0, то в группах функций 0, 1, 2, 3 (описываются инже) уравнения для Xи Yпримут вид (с учетом того, что операция инвертирования происходит в мультиплексорах):

Х=а1*b1 Va0*b0, Y = al • b1 V (a1 V b1) (a0 V b0).

В группах функций 4, 5, 6, 7 К=1, а X определяется из сравнения с нулем результата логической операции, причем Х=0, если результат логической операции равен нулю.

Во всех случаях информация на выходе переноса СО определяется из уравнения С0 = C1*Y V X*Y.

Отдельный выход АЛУ поступает иа регистр адреса памяти (РА) и с него через выходной буферный каскад (на три состояния) — на выходную шииу А. Обычно РА и шина Аиспользуются для пересылки адресов во внешнюю главную память. Регистр РА и шина Амогут быть использованы также для выборки внешнего устройства при выполнении операции ввода/вывода.

В каждом микроцикле иа входы FЦПЭ поступает микрокоманда. Она декодируется, мультиплексоры выбирают операнды, и АЛУ производит нужную операцию. По отрицательному фронту синхроимпульса результат операции АЛУ либо помещается в аккумулятор, либо записывается в выбранный регистр CОЗУ. Кроме того, в некоторых операциях результат операции АЛУ записывается в РА. Новая микрокоманда может быть подана только с положительным фронтом синхроимпульса. При внешнем управлении синхросигналом ЦПЭ синхроимпульс в микроцикле может быть пропущен, и так как схемы переноса, сдвига и ускоренного переноса не синхронизируются, то их выходы в этом такте могут быть использованы для выполнения ряда проверок данных в аккумуляторе и СОЗУ. При операциях в отсутствие синхросигнала содержимое регистров не изменяется.

Содержание выполняемой микрокоманды определяется функциональной (F-группа) и регистровой (F-группа) группами, которые задаются кодом по F-шине. F-группа определяется тремя старшими разрядами данных F4—F6, а R-группа — четырьмя младшими разрядами F0—F3.

R-группа 1 включает регистры R0—R9, Т, АС и обозначается символом Rn, R-группа 2 и R-группа 3 содержат только регистр Т и аккумулятор АС; они обозначаются AT.

В большинстве случаев установка сигнала на входах шииы К в 1 или 0 является соответственно либо выборкой, либо отсутствием выборки аккумулятора в данной микрокоманде. Мнемоника микрокоманд включена в каждое описание для справочных целей и может быть использована как язык микроассемблера.

В табл. 2 приведены статические, а в табл. 3 - динамические параметры микросхемы К589ИК02.

Таблица 2

| Параметр |

Обозначение |

Значения параметров[max, (min)] |

Ток потребления, мА

|

Icc |

190 |

Входной ток низкого уровня при Uil = 0,45 В, мА:

|

Iil

|

|

для входов F0—F6, CLK,

КО. К1, ЕА, ED |

-0.25 |

для входов I0, I1, RI, Ml, МО

|

-1.5 |

для входа CI |

-40 |

Входной ток высокого уровня при Uih=5,25 В, мкА:

|

IH

|

|

для входов F0—F6, CLK, КО, К1, ЕА, ED |

40 |

для входов I0, I1, Rl, Ml, МО

|

60 |

для входа CI |

180 |

для входа С/ Выходное напряжение низкого уровня, В

|

Uol |

0.5 |

Выходное напряжение высокого уровня, В

|

Uoh |

(2.4) |

Выходной ток низкого уровня в состоянии «выключено» при Vol =0,45 В, мкА |

Iozl |

-100 |

Выходной ток высокого уровня в состоянии «выключено» при Uон =5,25 В, мкА

|

Iozh |

100 |

Таблица 3

| Параметр¹ |

Обозначение |

Значение параметров |

Время цикла, нс |

Tc |

100 |

70 |

- |

Длительность импульса, нс |

tW |

33 |

20 |

- |

Время установления сигнала на входах относительно сигнала на входе CLK. нс:

|

|

|

|

|

на входах F0—F6

|

tS (F-CLK, L) |

60 |

40 |

- |

на входах 10, I1, МО, Ml, КО, К1 |

St(1—CI.K. I.) |

50 |

30 |

- |

на входах Rl, CI |

tS(C1—CLK.L) |

27 |

13 |

- |

Время сохранения сигнала на входах относительно сигнала на входе CLK, нc: |

|

|

|

|

на входах F0—F6

|

tH (CLK. H-F) |

5 |

-2 |

- |

на входах 10, I1, МО, Ml, КО, К1 |

tH (CLK. L-I) |

5 |

-4 |

- |

на входах Rl, CI |

tН (CLK. t-CI) |

15 |

2 |

- |

Время задержки распространения сигнала, не: от входов F0—F6 до выходов X, Y, R0

|

tР (F-X) tР |

- |

37 |

52 |

от входов 10, 11, МО, Ml, КО, К1 до выходов

X, Y, RO |

tP(I—X) |

- |

29 |

42 |

от положительного фронта синхроимпульса

CLK до выходов X, Y, RO

|

tР (CLK, H—X) |

- |

40 |

60 |

от отрицательного фронта синхроимпульса

CLK до выходов X, Y, RO

|

tР (CI.K, L-X) |

20 |

- |

- |

от положительного фронта синхроимпульса

CLK до выхода СО |

tР (CLK, H—CO) |

- |

48 |

70 |

от отрицательного фронта синхроимпульса

CLK до выхода СО |

tР (CLK, L—CO) |

20 |

- |

- |

от входов F0—F6 до выхода СО |

tР(F — СО) |

- |

43 |

65 |

от входов 10, 11, МО, Ml, КО, К1 до выхода СО |

tР (I-CO) |

- |

30 |

55 |

от входа СI до выхода СО |

Р(СI — СО) |

- |

14 |

25 |

от отрицательного фронта синхроимпульса

CLK до выходов АО, А1, DO, D1 |

Р (CLK. L — AD) |

5 |

32 |

50 |

Время задержки перехода от входов ЕА, ED до выходов АО, Al, DO, D1, нc |

tDE(Е-AD) |

- |

12 |

25 |

|