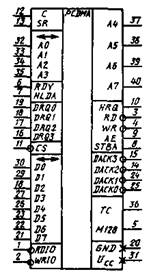

Микросхема KP580BT57

Микросхема KP580BT57 - четырехканальный программируемый контроллер прямого доступа к памяти (ПД), предназначен для высокоскоростного обмена данными между памятью системы и периферийными устройствами путем генерации массива последовательных метров заданного массива адресов ячеек памяти н управляющих сигналов Массив адресов, по которым происходит обмен данными между периферией и памятью, характеризуется начальным адресом, т. е. первым адресом начала обмена и числом циклов обращений к памяти После предоставления системной шины со стороны процессора микросхема может осуществить обмен массивом данных между памятью и периферийными устройствами без дальнейшего вмешательства процессора.

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

1 |

RDIO |

Вход/выход |

Чтение ввода/вывода |

2 |

WR IO |

Вход/выход |

Запись ввода/вывода |

3 |

RD |

Выход |

Чтение памяти |

4 |

WR |

Выход |

Запись памяти |

5 |

М128 |

Выход |

Модуль 128 |

6 |

RDY |

Вход |

Сигнал «Готовность» |

7 |

HLDA |

Вход |

Сигнал «Подтверждение захвата» |

8 |

STBA |

Выход |

Стробирующий сигнал адреса |

9 |

АЕ |

Выход |

Разрешение адреса |

10 |

HRQ |

Выход |

Запрос захвата |

11 |

CS |

Вход |

Выбор микросхемы |

12 |

С |

Вход |

Тактовый сигнал |

13 |

SR |

Вход |

Сигнал «Установка» |

25,24, 14, 15 |

DACK0—DACK3 |

Выходы |

Подтверждение прямого доступа к памяти каналов

о-з- |

19,18, 17, 16 |

DRQ0—DRQ3 |

Входы |

Запрос прямого доступа к памяти каналов 0—3 |

20 |

GND |

= |

Общий |

30,29, 28 27 |

D0—D7 |

Входы

выходы |

Канал данных |

26,23, 22, 21 |

|

|

|

31 |

Ucc |

— |

Напряжение питания |

32—35 |

АО—АЗ |

Входы выходы |

Канал адреса |

36 |

ТС |

Выход |

Конец счета |

37-40 |

А4-А7 |

Выходы |

Канал адреса |

Каждый из четырех каналов микросхемы обеспечивает адресацию (путем инкрементирования выработанного адреса) внешней памяти массивами объемом до 16К байт с возможностью задания любого из 64К начальных адресов. Условное графическое обозначение микросхемы, назначение выводов, структурная схема. Каналы приема запросов ПД предназначены для приема и привязки несинхронных сигналов прямого доступа к памяти DRQ0— DRQ3, маскирования входов и выдачи сигналов подтверждения запроса прямого доступа к памяти DACK0—DACK3. Каждый канал принимает запрос через свой вход DRQ и выдает сигнал «Подтверждение запроса» ПД через соответствующий выход. Устройство управления управляет последовательностью операций в течение всех циклов ПД путем генерации соответствующих управляющих сигналов. Устройство осуществляет переход микросхемы из состояния ожидания в состояние обслуживания по сигналу HLDA, поступившему из процессора, вырабатывает и передает внешние сигналы на следующие выводы: выход HRQ (запрос захвата) запрашивает управление системной шиной. В системе с одной микросхемой этот выход должен быть подключен ко входу «Захват» микросхемы КР580ВМ8ОА; вход HLDA (подтверждение захвата) получает от КР580ВМ80А сигнал, который свидетельствует, что микросхема КР580ВТ57 может приступать к управлению системными шинами, вход С (тактовый сигнал), на который подаются тактовые импульсы С2 от тактового генератора микропроцессорной системы, выход STBA (стробирующий сигнал адреса) стробирует старший байт адреса памяти, передаваемый через шину данных; выход АЕ (разрешение адреса) указывает системе, что происходят циклы ПД. Он может быть использован в системе для блокировки адресной шины в устройствах, не участвующих ч ПД; выход ТС (конец счета) указывает выбранному в настоящий момент периферийному устройству, что текущий цикл ПД должен быть последним для этого массива данных. Если разряд разрешения «КС-стоп» в регистре режима (РгР) установлен в 1, то выбранный канал будет автоматически запрещен в конце этого цикла ПД, т. е. в конце передачи массива данных Вывод активизируется (устанавливается в 1), когда содержимое 14-разрядного регистра циклов (РгЦ) в данном канале устанавливается в 0. 14 разрядов РгЦ должны быть загружены числом N— 1, где /V— нужное число циклон ПД.

выход М128 (маркер по модулю 128) указывает выбранному периферийному устройству, что текущий цикл ПД является 128-м или кратным 128 от конца массива данных. Если общее число циклов ПД N делится на 128 и РгЦ загружен числом N—1, то сигнал Ml 28 появляется на 128-м и каждом кратном 128 цикле от конца массива данных, вход RDY (готовность) асинхронный и используется для удлинения циклов записи в память (чтение из памяти) путем ввода микросхемы с помощью сигнала «Готовность» в состояние ожидания, если выбранная память требует более длинных циклов. выводы АО—A3 — адресные шины. Они являются трех стабильными выходами и устанавливают разряды 0—3 16-разрядного адреса памяти, генерируемого микросхемой во время всех циклов ПД. Схема установки режима хранит информацию о запрограммированных режимах: автозагрузки; КС-стоп; удлиненной записи: обычной записи; циклического сдвига приоритетов; фиксированного приоритета. Кроме того, разряды 0—3 регистра установки режима разрешают работу каждого из каналов. Регистр установки режима обычно загружается после того, как установлены регистр адреса (РгА) и регистр циклов (РгЦ). Регистр установки режима сбрасывается путем подачи сигнала на вход RS, что приводит к запрету работы всех каналов во всех режимах и предотвращает конфликты на шинах при подаче напряжения питания. Пользоваться каналами запрещается до тех пор, пока РгА и РгЦ не будут загружены необходимыми числами. В противном случае случайный запрос ПД (DRQ) от периферийного устройства может вызвать цикл ПД, что приведет к порче данных в памяти Состояние 1 в разряде 4 РгР устанавливает режим циклического сдвига приоритетов В этом режиме после каждого цикла ПД (но не каждого запроса ПД) приоритет каждого канала изменяется. Канал, который только что был обслужен, будет иметь самый низкий приоритет, а остальные каналы получат приоритет, следующий по уровню, как показано в табл. 3.24. Если разряд 4 установлен в 0, каждый канал ПД имеет фиксированный приоритет В режиме фиксированных приоритетов канал О имеет .наивысший приоритет, а канал 3 — самый низкий. Циклический сдвиг приоритетов предотвращает монополизацию одного из каналов ПД, последовательность циклов ПД будет обслуживать различные каналы, если разрешено обслуживание более одного канала Все операции ПД начинаются с первоначального присвоения каналу 0 наивысшего приоритета для перво10 цикла ПД. Состояние 1 в разряде 5 РгР устанавливает режим удлиненной записи В этом случае продолжительность сигналов WR и WRIO увеличивается путем более ранней их активизации в цикле ПД Передача данных в микропроцессорной системе на основе БИС КР580ВМ80А реализуется асинхронно, чтобы можно было использовать различные типы памяти и устройств ввода/вывода с различным временем доступа к памяти Если к устройству в указанный интервал времени доступ невозможен, то оно выдает в микросхему сигнал «Отсутствие готовности», тем самым заставляя ее войти в один или более тактов ожидания готовности Некоторые устройства отличаются достаточным быстродействием, чтобы получить к ним доступ без использования тактов ожидания готовности Для этого такие устройства должны генерировать свой сигнал «Готовности одновременно с появлением фронта сигнала WR или WRIO Однако в процессе формирования сигнала «Готовность» он задерживается, что может заставить микросхему войти в такт ожидания готовности Для вычислительных систем с этим типом устройств режим удлиненной записи обеспечивает другие временные соотношения для сигналов WR и WRIO, которые дают возможность устройствам раньше выдать сигнал «Готовность» и, следовательно, исключить 1акты ожидания для микросхемы, что увеличивает пропускную способность системы. Состояние 1 в разряде 6 РгР устанавливает режим «КС-стоп», при котором после появления сигнала ТС обслуженный канал ПД оказывается запрещенным В результате автоматически прекращаются всякие операции ПД в данном канале Разряд разрешения для данного канала должен быть перепрограммирован для продолжения или начала следующей операции ПД Если разряд 6 установлен в 0, то появление сигнала ТС не запрещает дальнейшее использование канала В этом случае сигнал информирует периферию об окончании операции ПД При наличии 1 в разряде 7 РгР устанавливается режим автозагрузки. Этот режим позволяет каналу 2 многократно передавать массив данных без программного вмешательства Регистры канала 2 устанавливаются, как обычно, для одной передачи массива. Регистры канала 3 в это время хранят параметры массива для переустановки регистров канала 2 (начальный адрес ПД, число циклов и направление передачи) После первой передачи массива данных через канал 2 и появления сигнала ТС параметры, хранимые в регистрах канала 3, автоматически загружаются в соответствующие регистры канала 2 Заметим, что возможности режима «КС-стоп» не воздействуют на канал 2, когда разряд 7 установлен в 1 Если разряд 7 установлен в 1, то начальные параметры для канала 2 автоматически дублируются в регистрах канала 3 при программировании канала 2. Это обеспечивает многократную передачу массива программированием только одного канала Операция многократной передачи массива может быть использована для регенерации изображения на электронно-лучевой трубке. Каналы 2 и 3 могут быть загружены также разными параметрами при условии, что канал 2 загружается раньше, чем канал 3 Следует заметить, что в ре жиме автозагрузки доступен для работы канал 3, если нет запроса ПД по каналу 2 и разряд разрешения каиала 3 РгР установлен в 1, но использование этого канала будет изменять значения параметров, которые должны загрузиться в канал 2. При использовании режима автозагрузки для операций по связыванию массивов данных (цепочка данных) надо перезагружать программно регистры канала 3 новыми параметрами для передачи следующего массива данных Каждый раз, когда в микросхеме происходит подмена данных канала 2 содержимым канала 3, в регистре состояния (РгС) аппаратно устанавливается разряд 4 «Флаг обновления данных» При этом подмена происходит с сохранением информации в регистрах канала 3 Повторный запуск канала 2 происходит в начале следующего цикла ПД канала 2 после появления сигнала ТС Это первый цикл ПД нового массива данных для канала 2. Разряд «Флаг обновления данных» в РгС сбрасывается аппаратно в конце этого цикла Для операций по связыванию массивов данных разряд «Флаг обновления данных» в регистре состояния каналов может контролироваться микросхемой КР58ОВМ80А, чтобы определить, когда параметры следующего массива данных могут быть гарантированно загружены в канал 3 В разрядах 0—3 РгС аппаратно устанавливается «Флаг завершения обслуживания» по соответствующему каналу после выработки сигнала ТС «Флаг завершения обслуживания» может также контролироваться процессором, однако в результате считывания флаг сбрасывается «Флаг завершения обслуживания» и «Флаг обновления данных» в РгС могут быть сброшены также сигналом SR или отказом от режима автозагрузки путем перепрограммирования РгР Установка разрядов 0—3 регистра установки режимов разрешает работу каждого из каналов Если разряд установлен в 0, то соответствующий канал блокируется. Схема управления периферийными устройствами осуществляет прием, формирование и выдачу сигналов, обеспечивающих обмен информацией между процессором и микросхемой КР580ВТ57, между памятью и периферийными устройствами. Если процессор загружает или читает один из регистров микросхемы КР580ВТ57 (последняя является периферийным устройством на системной шине), то микросхема получает сигнал RD 10 или WR 10 при CS = 0, декодирует младшие адресные разряды АО—A3 и либо записывает содержимое шины данных на адресуемый разрядами АО—A3 регистр микросхемы (WR 10= =0), либо выдает содержимое этого регистра на шину данных при RD 10=0 В состоянии обслуживания, когда микро схема управляет системными шинами, схема генерирует сигналы RDI0 н WR (цикл записи ПД) или WR 10 h~RD (цикл чтения ПД), которые управляют каналом данных, связанным с периферийным устройством Если микросхема является периферийным устройством по отношению к процессору, то сигнал RD 10 = 0, поступивший на вход RD 10=0, разрешает считывание с 8-разрядного регистра состояния каналов или старшего (младшего) байта 16-разрядного регистра адреса, или регистра числа циклов. Если микросхема находится в состоянии программирования, то вывод WR 10 является входом, а сигнал WR /0=0 позволяет содержимое шины данных загрузить в 8-разрядный регистр установки режима или старший (младший) байт в 16-разрядный регистр адреса или регистр числа циклов. Четыре младшие адресные шины АО—A3 двунаправленные. В режиме программирования они являются входами, которые выбирают один из регистров микросхемы для считывания или записи информации В режиме обслуживания они являются выходами, на которых устанавливаются младшие четыре разряда lb-разрядного адреса памяти, 1енерируемого микросхемой. Буферная схема данных (БД) представляет собой 8 разрядную двунаправленную шину с тремя состояниями, соединяющую микросхе му с системной шиной данных Двунаправленная шина данных DO—D7 с тремя состояниями При программировании в режиме записи восемь бит данных для адреса, регистра числа циклов или регисг ра установки режима передаются через шину 1анных из процессора. При чтении процессором содержимого регистра адреса, регистра числа циклов или регистра состояния каналов данные передаются в процессор также через шину данных В течение циклов ПД (копа микросхема управляет системной шиной) она выдает старшие восемь разрядов адреса памяти (из одного из регистров адреса ЗУ) Эти разряды адреса выдаются в начале каждого цикла ПД Затем шина данных освобождается тля обмена данными между памятью и периферией в течение оставшейся части цикла ПД Необходимым условием для обслуживания канала прямого доступа к памяти является поступление на микросхему из периферии сиг нала запроса DRQ, в результате чего микро схема вырабатывает сигнал «Запрос захвата» HRQ для передачи его на процессор По получении от микропроцессора сигнала «Подтверждение захвата» HLDA микросхема осуществляет: управление системной шиной, подтверждение запроса периферийного устройства, которое подключено к каналу с наивысшим приоритетом, выдачу младших восьми разрядов адреса памяти на системные адресные шины АО—А7, а старших восьми разрядов адреса на шину данных DO—D7; генерацию соответствующих сигналов управления RD или WR 10, RD 10, WR, которые побуждают периферийное устройство по лучить байт данных из ячейки или передать его в ячейку памяти За один цикл работы микросхема передает одни байт данных, причем в первом цикле вырабатывается адрес ячейки, равный начальному адресу, а в каждом по следующем адрес увеличивается на 1 до тех пор, пока число циклов обращений к памяти не станет равным заданному Микросхема управляет системной шиной и повторяет последовательность передач до тех пор, пока периферийное устройство сохраняет свой запрос Так микросхема может передать массив данных в быстродействующее периферийное устройство или выбрать его из этого устройства в один прием Когда указанное количество байт передано, микросхема выдает сигнал «Конец счета» ТС, информируя о завершении передачи данных В процессе выполнения циклов ПД (системные шины находятся под управлением микро схемы) имеются три различных режима работы режим чтения ПД — обеспечивает передачу данных из памяти в периферию; режим записи ПД — обеспечивает передачу данных из периферии в память, режим проверки ПД — не включает передачу данных. Канал ПД в режиме проверки не генерирует сигналы управления RD, WR, RD 10, WR 10, что предотвращает передачу данных. Однако в каждом цикле ПД микросхема осуществляет управление системной шиной и подтверждает запросы периферии Периферия может использовать сигналы подтверждения для разрешения внутреннего доступа к каждому байту в массиве данных для того, чтобы выполнить некоторые операции проверки. Например, массив циклов проверки ПД может следовать за массивом циклов чтения ПД (из памяти в периферию) для того, чтобы разрешить периферийному устройству проверить вновь поступившие данные. После окончания запрограммированного числа циклов ПД, характеризующегося выработкой сигнала ТС, возможны следующие виды работы дальнейшее наращивание адреса путем прибавления 1 в каждом последующем цикле ПД, блокировка канала ПД (режим «КС-стоп»); повторение ранее выработанного массива адресов (режим автозагрузки). Приналичии двух и более запросов будет обслуживаться периферия с наивысшим приоритетом. Вид приоритета устанавливается в процессе программирования Имеется два вида установки приоритета фиксированный, когда канал 0 имеет наивысший приоритет, а канал 3 — самый низкий; циклический сдвиг приоритета, когда после каждого цикла ПД приоритет каждого канала изменяется. В процессе функционирования микросхемы путем программирования РгР можно заблокировать (замаскировать) запрос любого канала В процессе функционирования в составе микропроцессорной системы микросхема может находиться в одном из следующих состояний исходное, программирование; ожидание, обслуживание. В исходное состояние микросхема устанавливается после включения путем подачи на ее вход SR сигнала «Установка» В этом состоянии маскируются запросы всех каналов ПД, а трехстабильные буферные схемы системной шины АО—A3 переводятся в состояние приема информации В состоянии программирования микросхемы микропроцессор по системным шинам данных DO—D7 осуществляет запись в соответствующие регистры микросхемы исходных данных (начальные адреса и число циклов) и инструкции, определяющей режим работы микросхемы при циклах ПД При этом адресат приема информации микросхемой определяется кодом на системных шинах АО—A3 В состоянии ожидания микросхема находится от момента окончания программирования до получения сигнала «Подтверждение запроса захвата» HLDA или в промежутках между массивами циклов ПД в отсутствие запросов ПД В состоянии ожидания осуществляется прием сигналов DRQ и вырабатывается для микропроцессора сигнал «Запрос захвата» HRQ В этом состоянии системные шины находятся под управлением микропроцессора После получения от микропроцессора сигнала HLDA при наличии сигнала запроса DRQ микросхема вырабатывает сигнал DACK и переходит в состояние обслуживания В этом состоянии системные шины находятся под управлением микросхемы, которая осуществляет один из запрограммированных режимов ПД и генерирует набор управляющих сигналов, не обходимых для осуществления обмена данными между памятью и периферией Регистры микросхемы загружаются или с них считывается информация, если процессор выполняет команду записи или чтения путем обращения к микросхеме КР580ВТ57 и к соответствующим регистрам внутри микросхемы Для этого процессору необходимо выдать со ответствующие сигналы записи или чтения WR 10, RD 10 и на системные адресные шины выдать адрес регистра микросхемы В это время на шину данных подается необходимая информация для записи в регистры или же через шину данных читается информация из микросхемы Для установки состояния программирования необходимо также на микросхему подать сигнал CS = 0, получаемый обычно путем декодирования всех или .некоторых старших 1Й разрядов адреса А4—А15 (в зависимости от системной организации памяти и устройств ввода/вывода) Вход WR 10 (или WR при общем поле памяти и УВВ) указывает на запись в регистры микросхемы, а вход RD 10 (или RD) — на чтение из регистров Разряд A3 позволяет различить регистры каналов при А3=0, а при Л3=1—регистр установки режима (работает только на запись), и регистр состояния каналов (работает только на чтение) Три младших разряда АО—А2 указывают конкретный регистр канала Если адресуется регистр установки режима или регистр состояния каналов, то разряды АО—А2 должны быть установлены в 0 Когда адресуется регистр канала, разряд АО позволяет различить регистры адреса ПД (при Л = 0) и числа циклов (при А=\) Разряды Al, A2 позволяют определить номер канала Коды выборки регистров приведены в табл 3 25 В связи с тем, что регистры канала являются 16-разрядными, для их загрузки или чтения необходимо два программных командных цикла В микросхеме имеется триггер, который автоматически переключает цепи во время выполнения операции чтения или записи Этот триггер определяет доступ к старшему или младшему байгу регистра Сбрасывается триггер путем подачи сигнала н вход SR, а также всякий раз при загрузке регистра установки режима. Для обеспечения соответствующей синхронизации при обращениях к регистрам канала все команды, поступающие от процессора, должны появляться парами, причем всегда младший байт регистра должен получить доступ к_ памяти первым

Нельзя подавать сигнал CS до тех пор, пока сигнал RD 10 или WR 10 не станет активным, так как это может привести к ошибочному состоянию триггера. В системах, использующих прерывания, запросы прерывания должны быть запрещены в процессе программирования регистров канала, чтобы не было разделения парных команд записи или чтения регистров Временная диаграмма работы микросхемы при программировании в режиме записи, а, а в режиме чтения Внутренние операции микросхемы по переходу из состояния ожидания в состояние обслуживания могут быть выполнены в течение семи тактов Продолжительность тактов определяется тактовой частотой микросхемы Если микросхема не выполняет цикла ПД, то она находится в холостом такте SO до прихода сигнала запроса ПД. С приходом сигнала DRQ последний обрабатывается согласно установленному приоритету (фиксированному или циклическому) и вырабатывается сигнал HRQ По этому сигналу микросхема переходит к такту S1 Это положение будет сохраняться до прихода е процессора сигнала «Подтверждение захвата» HLDA. Таким образом, состояние ожидания характеризуется пребыванием микросхемы в тактах SO, St. При получении сигнала HLDA возбуждается шина DACK канала, имеющего запрос с наиболее высоким приоритетом Таким образом осуществляется выборка канала и соответствующего периферийного устройства для цикла ПД, и микросхема переходит к такту S2 Заметим, что сигнал HLDA должен оставаться с высоким уровнем напряжения до тех пор, пока не появится сигнал PACK при одном цикле ПД или оба сигнала DACK и ТС при передаче массива Если микросхема потеряет управление системными шинами, те если сигнал HLDA станет равным 0, то сигнал DACK будет сохраняться до окончания текущего цикла ПД. После этого циклы ПД прекращаются до тех пор, пока микросхема снова не получит управление системными шинами Каждый цикл ПД (состояние обслуживания) содержит не менее четырех тактов. S2, S3, S4, S5. Если время доступа к памяти и УВВ, включенных в систему, недостаточно для передачи байта в указанное число тактов, то между тактами S4 и S5 вводится один и более тактов ожидания SWI. Использование удлиненной записи может в некоторых случаях исключить такты ожидания. Если в циклах ПД осуществляется режим проверки, то сигнал RDY не требуется. Временная диаграмма работы микросхемы ПД |