PCI

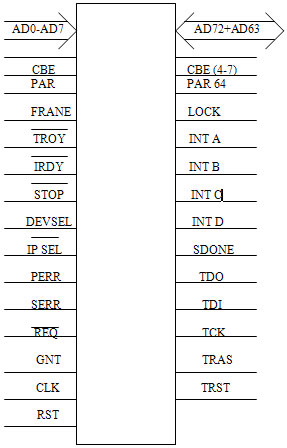

Высокоскоростной интерфейс : 32-64 разрядный с мультеплексированной ША данных.

Назначение :

Универсальный интерфейс (соединение процессора с переферийными элементами и системой процессора памяти). Имеется встроенная поддержка кэширования (механизм слежения за шиной – интерференция данных).

Скорость : 33,66,133 МГц.

Пересылки : 32 и 64 бит , следовательно ширина ШД : 4-8 байт

Групповые пересылки разрешаются (Burst) . Реализован скрытый арбитраж : арбитраж осуществляется в то время когда когда на шину идут пересылки (время не тратится). Низкая стоимость , определяется малым числом выводов (49 для ”мастер” и 47 для Slave). Простота использования : реализована функция авто конфигурирования системы. Высокая надёжность : при пересылки осуществляется контроль чёткости адреса данных.

RST – сброс

AD – мультиплексированная шина команд и подтверждение байтов

SBE – подтверждение байтов

PAR – чётность контроль : контроллируются все выше указанные разряды

FRAME – уравляется мастером или задатчиком шин ; указывает начало и конец пересылок

TRDY – устройство подчинено и готово к обмену

IRDY – мастер (инициатор) готов к обмену

STOP – требование к мастеру прекратить пересылки

hock – сигнал захвата шины

DEVSEL – подчинённое устр-во (slave) распознало свой адрес

IDSEL – сигнал выбора устр-ва при инициализации системы

PERR – ошибка чётности

SERR – системная ошибка

REQ – запрос мастера к арбитру на обладание шины

GNT – подтверждение арбитра мастеру , что шина ему предоставлена

INT A,B,C,D – запрос на преревание

Основные циклы

1.Чтение (система с изолированной шиной и каждое устр-во имеет свой дешефратор адреса)

а) позитивная дешефрация (устр-во опознаёт свой собственный диапазон адресов)

б) вычитательная дешифрация (на шине 1 устр-во , которое отвечает за все остальные не заполненные адреса) .

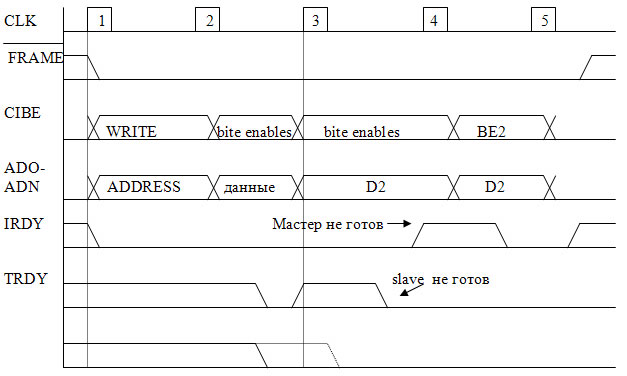

PCI : Реализованный синхронный алгоритм обмена синхронного сигнала – даёт приемушество в быстродействии

IRDY = 1 и FRAME = 1 - обмен завершён.

Такт 1 : инициатор (мастер шины выставляет сигнал FRAME , который говорит ,что шина захвачена и выставлен сигнал IRDy ,следовательно устройство (мастер ) готово к обмену.

Такт 2 : к момену выставления фронта ,мастер выставляет команду WRITE и адрес ADDRESS ,по которому осуществляется обращение .

Такт 3 : в промежутке между татктом 2 и татктом 3 3slave определяет , что обращение осуществлено к нему и выставлен знак DEVSEV и TRDY.

Такт 3 : активное устр-во выставляет данные на ШД и выставляет сигнал Byte Enables, который подтверждает каждый из передоваемых байтов (читакт первую порцию данных адресованное устр-ву D1).

Такт 4: Slave не готов к обмену и выставляет сигнал TRDY и активное устр-во данные ен передаёт .

Такт 5 : Мастер не готов и выставляет сигнал об этом и Slave не принимает данные. Т5 –Т6 : оба устр-ва готовы к обмену и мастер выставляет порцию данных и Byte Enables Т7: цикл завершается: выыставляетоднавременно пару сигналов в IRDY =1 и FRAME=1 – цикл завешон.

Арбитраж: скрытый в PCI : освмещённый реальный арбитраж с работой др. устр-в . У каждого устр-ва сигналы REQ , GNT свои.

Активное устр-во выдаёт сигнал REQ на арбитр по своей линии . Арбитр определяет какое устр- во имеет наиболее высокий приоритет и по линии выдаёт сигнал GNT этому устр-ву.Активное устр-во выставляет сигнал FRAME ,что устр-во захвачено и осуществляет обмен.

Особенности :

1) Групповая пересылка

2) Встроенная поддержка кэширования

Неудобства – существование мостов и необходимость реализовать сопрягающее устройство . |