Микросхема КМ1811ВТ1

KH1811BMI с оперативной памятью емкостью до 4М байт.

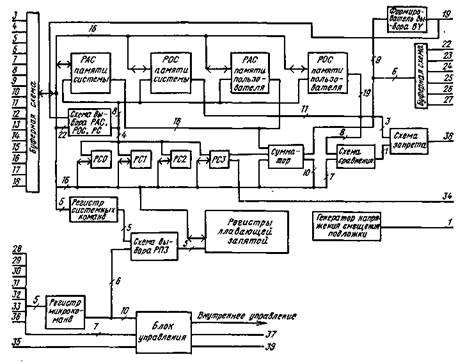

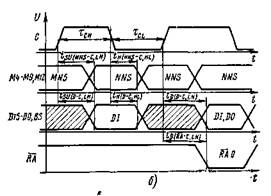

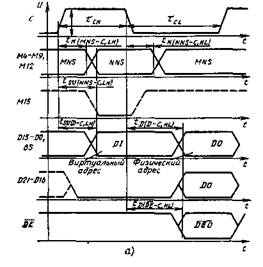

Условное графическое обозначение микросхемы приведено на рис. 1, назначение выводов— в табл. 1, структурная схема показана на рис. 2, временные диаграммы входных и выходных сигналов — на рис. 3, а (режим преобразования адреса) и 3,б (режим обмена данными).

В состав микросхемы КМ1811ВТ1 входят: 16 16-разрядных регистров адресов страниц (РАС) памяти системы; 10 16-разрядных регистров описания страниц (РОС) памяти системы; 16 16-разрядиых РАС памяти пользователя; 12 16-разрядных РОС памяти пользователя; 4 16-разрядных регистра состояний (РСО—РС4); регистры системных команд и микрокоманд; регистры плавающей запятой; логика управления.

Микросхема осуществляет преобразование 16-разрядных логических адресов в 18- либо 22-разрядные физические адреса. Это обеспечивает расширение объема адресуемой памяти с 64 до 256К байт либо до 4М байт соответственно. Для системного режима и режима пользователя перемещение адресов осуществляется Микросхема КМ 1811 ВТ 1 — диспетчер памяти, обеспечивает стыковку микросхемы постранично с длиной страницы от 64 байт до 8К байт, с шагом 64 байта.

|

Рис 1 |

Таблица 1

Вывод

/ |

Обозначение

GU |

Тип вывода Выход |

Функциональное назначение выводов

Напряжение внутреннего генератора смещения подложки |

2 |

С |

Вход |

Тактовые импульсы |

3—18 |

D0—D15 |

Вход/выход |

Совмещенная шина адреса (разряды 15—0) и данных |

19 |

BS |

Вход/выход |

Сигнал «Выбор ВУ». Входной сигнал разрешает обращение к внутренним регистрам. Выходной сигнал вырабатывается в случае формирования физического адреса старших 8К байт адресного пространства |

20 |

GND |

— |

Общий |

21 |

Ucс2 |

— |

Напряжение питания +12 В |

22—27 |

DZ16—DZ21 |

Выход |

Шина адреса, разряды 21 — 16 |

28—33 |

М4—М9 |

Вход |

Шина микрокоманд, разряды 4—9 |

34 |

МЕ |

Выход |

Преобразование адреса |

35 |

EZ |

Вход |

Установка выходов в высокоомное состояние |

36 |

М12 |

Вход |

Шина микрокоманд, разряд 12 |

37 |

RA |

Выход |

Сигнал «Готово». Означает готовность к приему информации |

38 |

DE |

Выход |

Сигнал «Запрет». Сигнал о неправильном обращении к памяти |

39 |

М15 |

Выход |

Шина микрокоманд, разряд 15. Означает, что происходит выдача физического адреса |

40 |

Ucc |

~ |

Напряжение питания +5 В |

|

Рис 2 |

Кроме того, микросхема осуществляет функции защиты памяти и обеспечивает: разделение областей адресного пространства, используемого в системном режиме н режиме пользователя; различные виды доступа к каждой перемещаемой странице — страница без доступа, страница только для считывания, страница для записи и считывания.

В качестве исходной информации при преобразовании адресов и защите памяти в диспетчере используется содержимое РАС и РОС памяти системы и пользователя; РАС и РОС разделены на группы. Одна группа используется при работе микросхемы в системном режиме, другая — в режиме пользователя. Каждая группа регистров содержит 16-разрядный регистр адреса страницы и регистр описания страницы. Кроме того, имеются четыре регистра состояния (PC0 — РСЗ), которые используются в механизме управления памятью. Информация, заключенная в РСЗ, указывает разрядность формируемого физического адреса: 18 или 22.

|

|

Рис 3 (а) |

Рис 3(а) |

Таблица 2

Параметр |

Обозначение |

Значения параметров [макс/(мни.)] |

Режим измерения |

Ток потребления от источника Ucc2, мА |

1сс1 |

75 |

Uсс, = 5,25В, Uсс2=12,6В |

Ток потребления от источника Uca, мА |

1ссг |

45 |

Ucc1 = 5,25B, Uсс2=12,6В |

Выходное напряжение низкого уровня по выводам ШАД, В |

UoL, D |

0,5 |

Iol = 1,5 мА |

Выходное напряжение высокого уровня по выводам ШАД, В |

UoH, D |

(2,4) |

Iон = 0,2 мА |

Выходное напряжение низкого уровня по выводам BS, ME, RA, DE, M15, В |

UoL |

0,5 |

Iol = 2,5 мА |

Выходное напряжение высокого уровня по выводам BS, ME, RA, DEM15, В |

U он |

(2,4) |

Iо н = 0,2 мА |

Входное напряжение низкого уровня по выводу 55, В |

UlL, BS |

0,8 |

|

Входное напряжение высокого уровня по выводу BS, В |

Um, BS |

(2,4) |

|

Таблица 3

Параметр |

Обозначение |

Значения параметро

[макс.

(мин)] |

Время установления нанокоманды,

нс |

tsU(NNS—C, LH) |

110 |

Время сохранения нанокоманды, нн |

H(NNS -С, HL) |

(20) |

Время установления входных данных, НС |

tSU(D-C. LH) |

110 |

Время сохранения входных данных,

НС |

tН(0 — С, HL) |

(20) |

Время задержки входных данных,

НС |

tD(D— С, LH) |

180 |

Время задержки сигнала «Готово»,

НС |

tD(rA — C, LH) |

180 |

Время сохранения микрокоманды, нс |

tH(MNS — C, LH) |

(20) |

Время задержки выходных данных,

НС |

td(D— С, HL) |

260 |

Время задержки сигнала «Запрет», не |

tD(DE-C, HL) |

250 |

Старшие три разряда логического адреса, принимаемого по ШАД, определяют, какая именно нз восьми пар регистров РАС/РОС для каждого режима будет использоваться. Содержимое выбранного регистра РАС или РОС поступает на вход сумматора, на другой вход поступают разряды 12 — 6 логического адреса.

Сумматор формирует разряды 21 — 6 физического адреса. Разряды 5 — 0 физического адреса соответствуют разрядам 5 — 0 логического адреса.

По сигналу «Выбор ВУ» формируется напряжение высокого уровня, если физический адрес попадает в старшие 8К адресного пространства.

При преобразовании адреса на выходе М15 устанавливается напряжение низкого уровня; это означает, что в ШАД в следующий полутакт будет выдан физический адрес.

Схема сравнения совместно с РОС и логикой запрета непосредственно участвует в ре ализации функций защиты памяти. При нарушении правил доступа формируется сигнал «Запрет» (ДE), а в регистрах состояния запоминается информация, вызвавшая запрет.

Сигнал «Готово» (RA) является ответом микросхемы при обращении к ее регистрам РАС, РОС и PC.

Дополнительной функцией микросхемы является участие в выполнении операций с плавающей запятой для обеспечения временного хранения и оперативной выдачи соответствующей информации. Для этого используется 42 16-разрядных регистров, адрес каждого из которых выбирается определенными комбинациями системных микрокоманд.

Электрические статические параметры КМ1811ВТ1 приведены в табл. 2, динамические— в табл. 3. |