Микросхема КН1811ВМ1

Микросхема КН1811ВМ1 представляет собой центральный процессорный элемент, выполняющий арифметические и логические операции над 16-разрядными операндами.

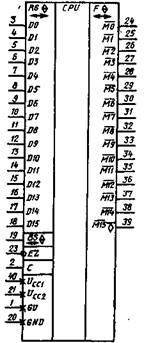

Условное графическое обозначение микросхемы КН1811ВМ1 приведено на рис.1,

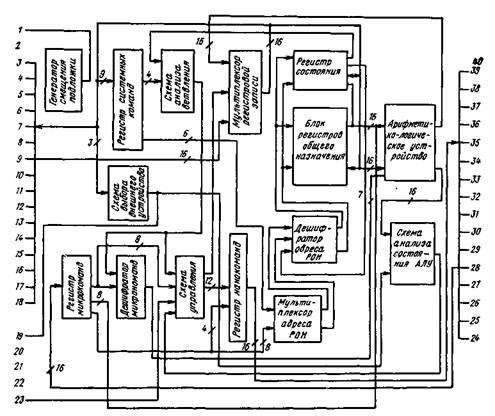

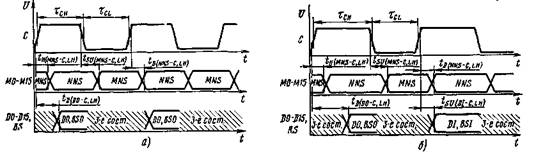

назначение выводов -- в табл. 1, структурная схема показана на рис. 2, временная диаграмма входных и выходных сигналов на рис. 3.

В состав микросхемы входят: 16-разрядное арифметико-логическое устройство (АЛУ); блок регистров общего назначения (РОН); мультиплексор регистровой записи; мультиплексор и дешифратор адреса РОН; регистр системных команд (РСК); регистр микрокоманд (РМК); регистр нанокоманд (РНК); схема анализа ветвления; дешифратор микрокоманд; схема управления; схема выбора банка.

Микросхема имеет два 16-разрядных двунаправленных информационных канала: шину адреса и данных (ШАД) D15—DOи шину микроканала (ШМК) М15—МО.

По ШМК при низком уровне тактового сигнала xclпоступает микрокоманда MNS, которая принимается микросхемой. Входы/выходы ШАД в это время находятся в высокоомном (3-м) состоянии.

При высоком уровне тактового сигнала тсн в ШМК осуществляется вывод нанокомаиды NNS, которая удерживается в ШМК до прихода очередной микрокоманды. По ШАД в это время может происходить ввод или вывод информации.

Информация, поступающая по ШАД, заносится в блок РОН, который предназначен для временного хранения информации и ее оперативной передачи в АЛУ и внешним схемам. Регистровый блок состоит из 18 16-разрядных регистров. Десять регистров программно-доступны. К ним относятся регистры общего назначения, регистр—указатель стека системного режима, регистр—указатель стека режима пользователя и программный счетчик. Семь регистров используются в качестве временной оперативной памяти для хранения информации прн выполнении сложных микропрограммных операций. Один регистр используется только для хранения слова состояния процессора.

|

Рис 1 |

Таблица 1

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

1 |

GU |

ВЫХОД |

Напряжение внутреннего генератора смещения подложки |

2 |

С |

Вход |

Тактовые импульсы |

3—18 |

D0—D15 |

Вход/выход |

Совмещенная шнна адреса и данных |

19 |

BS |

Вход/выход |

Сигнал «Выбор ВУ». Входной сигнал поступает в случае адресования к старшим 8К байт адресного пространства. Выходной сигнал разрешает обращение к диспетчеру памяти |

20 |

GND |

__ |

Общий (шина «земля») |

21 |

U СС 2 |

- |

Напряжение питания +12 В |

23 |

EZ |

Вход |

Установка выходов в высокоомное состояние |

24—39 |

М0—М15 |

Вход'выход |

Шина микрокоманд |

40 |

Ucci |

|

Напряжение питания +5 В |

|

Рис 2 |

Регистровый блок имеет двухканальную (двух портовую) структуру. Порт В предназначен только для чтения, а порт А может использоваться как для записи, так и для чтения информации. Такая структура регистрового блока позволяет иметь минимум регистров, необходимых для эмуляции системных команд, и сократить время выполнения команд. Порт Л регистрового блока связан с магистральной ШАД. Через эту шину осуществляется передача данных, хранящихся в регистровом блоке, внешним схемам, АЛУ, а также загрузка программно-доступных регистров и регистра системных команд. Вывод информации из регистрового блока происходит при высоком уровне напряжения тактового сигнала, запись информации— при низком уровне.

|

Рис 3 |

На входы АЛУ информация поступает из блока РОН и регистра микрокоманд.

Блок АЛУ выполняет арифметические операции над двоичными и двоично-дрсятнчными числами, логические операции, операции циклического и арифметического сдвигов вправо/ влево, пересылки байтов и слов, проверки и установки бит; АЛУ имеет 16-разрядную структуру.

Каждый разряд АЛУ состоит из универсального программируемого логического модуля, полусумматора, логики поразрядного сдвига, логики переноса в старший и младший разряды, выходных формирователей. Кроме того, в состав АЛУ входит логический блок преобразования данных и аппаратного наращивания адреса. Информация, подлежащая обработке, поступает в АЛУ по шинам порта А и порта В регистрового блока. Результат операции записывается в регистр по адресу порта А. В течение одного тактового цикла (290 не) АЛУ производит операцию и помещает результат в регистровый блок. В качестве входной информации для АЛУ может быть содержимое двух регистров при регистровой микрокоманде, одного регистра и литерала (вид данных, содержащийся в микрокоманде) для литеральных микрокоманд. Литерал поступает на входы АЛУ по шинам порта В младшего байта блока РОН. АЛУ всегда оперирует 16-разрядными словами. В случае байтовых операций содержимое одного из байтов восстанавливается. В процессе выполнения любой микрооперации входная информация АЛУ, поступающая по шинам порта А, выдается в ШАД. Выходная информация АЛУ передается в блок РОН с помощью мультиплексора регистровой записи, который управляет обменом информацией между АЛУ, блоком РОН и ШАД.

Обращение к регистрам общего назначения может осуществляться микропрограммным и программным способами. Организацию обращения к регистровому блоку осуществляют блоки: дешифратор адреса РОН, мультиплексор адреса РОН, регистр состояния, регистр системных команд.

В случае обращения к регистровому блоку микропрограммным способом адрес регистров по порту А и порту В выбирается из адресного поля текущей микрокоманды. Поле разрядов 0—3 (поле А) служит адресом регистра порта А, поле разрядов 4—7 (поле В) служит адресом регистра порта В для двухадресных микрокоманд. При использовании одноадресной микрокоманды обращение осуществляется только по полю А (разряды 0—3) микрокоманды; при этом по полю В включается защита по обращению.

При обращении к регистровому блоку программным путем в поле адреса порта А н порта В в микрокоманде устанавливается признак программного обращения Адрес регистра в jtom случае выбирается из регистра системных команд (адресное поле системной команды)

Таблица 2

Параметр

Ток потребления от источника Ucci, мА |

Обозначение Ucci |

Значения параметров

мин. макс.

— 90 |

Режим измерения

Ucc1 = 5,25 В, Uсс2=12.6 В |

Ток потребления от нсточинка Ucc2, мА |

lcc2 |

— 41 |

Uсс| = 5,25 В,

UСС2=12,6 В |

Выходное напряжение низкого уровня по выводам ШАД В |

UOL, D |

— 0,5 |

Uol = 1,5 мА |

Выходное напряжение высокого уровня по выводам ШАД, В |

UОН, D |

2,4 — |

Uон = 0,2 мА |

Выходное напряжение низкого уровня по выводам шмк, в |

UOh, М |

- 0,5 |

Uоь = 2,5 мА |

Выгодное напряжение высокого уровня по выводам шмк, в |

Uoh, м |

3,5 — |

Uон = 0,2 мА |

Выходное напряжение низкого уровня по выводу BS, В |

UOL, BS |

— 0,5 |

UloL — i,5 мА |

Выходное напряжение высокого уровня по выходу BS, В |

Uoh, bs |

3.4 — |

Uон = 0,2 мА |

Входное напряжение низкого уровня по выводу BS, В |

UIL, BS |

— 0,8 |

|

Входное напряжение высокого уровня по выводу BS, В |

UiH, bs |

2,4 — |

|

Таблица 3

Параметр |

Обозначение |

Зна пара

мнн |

ченни метров

макс |

Время сохранения сигнала микрокоманды, ис |

^Hl^MNS — C, LH) |

20 |

50 |

Время установления сигнала микрокоманды, не |

lSmM\S-C, HL) |

50 |

ПО |

Время задержки сигнала нанокоманды, не |

'o(\A'S—С, LH) |

|

95 110 |

|

^£>(£Ю —С, LH) |

~ |

185 |

Время установления сигнала входных данных, не |

?St/(D/ —C, LH) |

|

75 |

При обращении к регистрам-указателям стека, имеющим один н тот же микропрограммный и программный адрес, используется дополнительный адрес регистра состояния

Подключение входов дешифратора адреса к соответствующим шинам регистра системных команд или регистра микрокоманд осуществляется посредством мультиплексора адреса РОН Управление производится полем адреса микрокоманды

В процессе выполнения арифметических, логических операций, операций сдвига, пере сылки, сравнения и проверки бит результат операций анализируется логикой и при получении переполнения, нулевого результата, переноса, отрицательного результата выдается информация для записи в соответствующий разряд регистра состояния

Регистр состоянии (на структурной схеме рис 2 условно выделен из блока РОН) выполняет функции хранения и оперативной выдачи информации слова состояния процессора логике внутреннего управления работой микросхемы КН1811ВМ1, внешним схемам и другим микросхемам комплекта Кроме перечисленных данных регистр состояний хранит так же информацию о режиме работы системы (текущем и предыдущем)

Анализ слова состояния и текущей команды осуществляет схема анализа ветвления, вырабатывающая соответствующие сигналы для дешифратора микрокоманд и управляющей логики

Регистры системных команд, микрокоманд и нанокоманд обеспечивают хранение и оперативную выдачу соответствующей информации Под нанокомандой понимается 16-разрядное слово, выводимое в ШМК для управления другими микросхемами МПК, а также внешними устройствами Схема выбора внешнего устройства обеспечивает формирование сигнала, характеризующего адресный диапазон работы микросхемы Выходной сигнал вырабатывается при использовании старших 8К байт из 64К байт памяти и управляет работой микросхемы КМ1811ВТ1

На временной диаграмме входных и выходных сигналов (рис 3) показаны два режима работы базовый цикл — режим выполнения всех микроопераций, кроме операций ввода/вывода информации и режима преобразования адреса, цикл ввода вывода — режим ввода/вывода информации В режиме преобразования адреса прием сигнала по входу «Выбор ВУ» осуществляется при низком уровне тактового сигнала |