Микросхемы КН1811ВУ1, КН1811ВУ2, КН1811ВУЗ

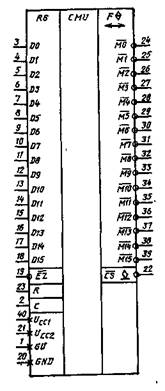

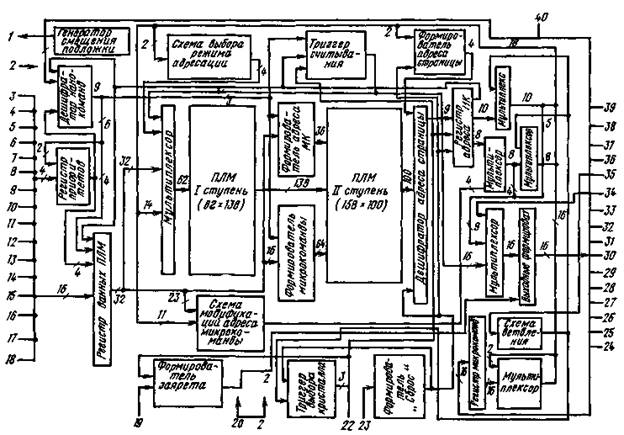

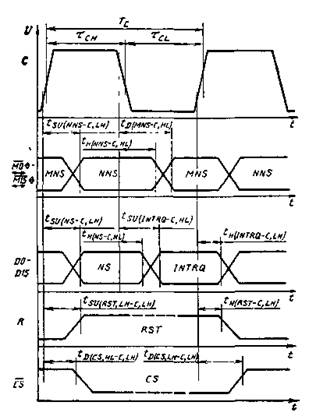

Все три микросхемы предназначены для управления микросхемой К.Н1811ВМ1 Условное графическое обозначение микросхем приведено на рис 1, назначение выводов в табл 1, структурная схема показана на рис 2 временная диаграмма входных и выходных сигналов — на рис 3

В состав микросхем входят 16-разрядный регистр данных ПЛМ (РД); 16-разрядный регистр микрокоманд (РМ), 9-разрядный регистр адреса микрокоманд (РАМ); дешифратор нанокоманд (ДН), логика модификации адреса микрокоманды (МА), логика ветвления микропрограммы (ВМ); логика приоритетов прерываний (ПП), логика выбора кристалла (ВК); программируется логическая матрица (ПЛМ)

Микросхемы имеют две 16-разрядные информационные шины шину адреса и данных ДО—Д15 (ШАД) и шину микрокоманд М0 — М15 (ШМК).

|

Рис 1 |

Таблица 1

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

1 |

GU |

Выход |

Напряжение внутреннего генератора смещения подложки |

2 |

С |

Вход |

Тактовые импульсы |

3—18 |

D0—D15 |

Вход |

Шина адреса и данных |

19 |

EZ |

Вход |

Установка выходов в высокоомное состояние |

20 |

GND |

|

Общий (шина «земля>) |

21 |

Ucс2 |

— |

Напряжение питания +12 В |

22 |

CS |

Выход |

Сигнал «Выбор кристалла Вырабатывается при работе данной микросхемы |

23 |

R |

Вход |

Сигнал «Сброс». Начальная установка адреса |

24—39 |

M0-M15 |

Вход/выход |

Шина микрокоманд |

40 |

U cc1 |

|

Напряжение питания +5 В |

|

Рис 2 |

|

Рис 3 |

При низком уровне тактового сигнала тсч. с выходов микросхемы КН18ПВУ1 в ШМК поступает 16-разрядная микрокоманда MNS. По шине ШАД в это время в РД могут поступать сигналы запросов прерываний 1NTRQ.

При высоком уровне тактового сигнала тсн по ШМК передается управляющая наиокоманда NNS. Шестиразрядное поле NNSпоступает на ДН, а одноразрядное поле NNS— на логику ВМ. По ШАД в это время в РД может поступать команда NSили информация о приоритетах прерываний из регистра состояния КН1811ВМ1.

Управляющая микропрограмма размещается в ПЛМ объемом 15 800 бит. ПЛМ представляет собой сочетание собственно программируемой логической матрицы объемом 133X32 разрядных слов и ПЗУ объемом 444X26 разрядных слов. Выборка микрокоманд из ПЛМ осуществляется под управлением команд (или данных о запросах прерываний), хранящихся в РД, н адресных полей микрокоманд, хранящихся в РАМ. Управляющее 16-разрядиое поле микрокоманды через мультиплексор и выходной формирователь выводится в ШМК и поступает в РМ. Адресное 9-разрядное поле микрокоманды через РАМ и мультиплексоры поступает по внутренней шине адреса на входной мильтиплексор ПЛМ и на логику МА. Для управления ветвлением микропрограммы адресное поле микрокоманды может быть изменено следующими четырьмя способами: разряды 0 — 3 определенных адресов изменяются логикой МА под управлением данных из РД;

разряды 0 — 7 любого адреса заменяют данными из разрядов 0 — 7 РМ под управлением логики ВМ (условное ветвление);

разряды 0 — 8 любого адреса генерируются формирователем адреса МК в соответствии с данными в РД;

разряды 0 — 8 адреса формируются в процессе выборки микрокоманды из программируемой логической матрицы с помощью логического сложения.

Управление вводом данных в РД и регистр ПП осуществляет дешифратор ианокоманд. Ввод информации о запросах прерываний в РД осуществляется автоматически в конце выполнения очередной команды программы. Прием сигналов INTRQпо входам D8—D12 «маскируется» данными, находящимися в регистре ПП.

К ШМК (в архитектурном максимуме МПК) может быть подключено до 16 микросхем управления. В каждом конкретном тактовом цикле «активной», т. е. участвующей в работе МПК, является только одна из них; выходы остальных находятся в высокоомном состоянии. Передача управления от «активной» микросхемы управления любой другой («пассивной») микросхеме управления осуществляется микрокомандами передачи управления. Микрокоманды передачи управления от «активной» микросхемы при низком уровне тактового сигнала принимаются всеми «пассивными» микросхемами управления в РМ. Логика ВК микросхемы, которой передается управление, обеспечивает выбор стартового адреса микропрограммы, записанной в ее ПЛМ, и формирует сигнал CSна выходе CS. Логика ВК микросхемы, которая передает управление, переводит ее выходы МО — М15 в высокоомное состояние и формирует соответствующий уровень сигнала CSдайной микросхемы.

Общее число реализуемых микрокоманд 83.

Набор микрокоманд делится на специфические группы микрокоманд:

арифметические, обеспечивающие выполнение операций над двоичными и двоичио-коди-роваиными десятичными числами — условное и безусловное сложение слов, байтов, условное и безусловное вычитание слов, байтов,сложение и вычитание с переносом, без переноса и др.;

логические — И, ИЛИ, ИЛИ — НЕ, исключающие ИЛИ слов, байтов, очистка, расширение или изменение знака, инвертирование слов, байтов и др.;

регистровые — пересылка слов, байтов, признаков, перестановка слов, байтов и др.;

сдвига — арифметический и циклический сдвиг влево, вправо слов, байтов, условный и безусловный сдвиг;

перехода — условный переход, безусловный переход;

инкремента, декремента — сложение с константой с наращиванием на 1, уменьшением на 1 и др.;

проверки и установки условий — проверка слов, байтов, разрядов, литералов и др.;

передачи управления;

ввода, вывода — ввод слов, байтов, литералов, вывод данных, вывод адресов слов, байтов, вывод слова состояния и др.

литеральные — операции, где одним из операндов является литеральная часть микрокоманды;

Таблица 2

Параметр |

Обозначение |

Значения параметров

[макс. (мни.)] |

Режим измерения |

Ток потребления от источника Ucc1, мА |

Icc1 |

50 |

Ucc1 = 5,25 В, Uсс2=12,6 В |

Ток потребления от источника Ucc, мА |

Icc2 |

50 |

Ucc1 = 5,25 В, UCc2=12.6 В |

Выходное напряжение низкого уровня по выводам ШМК, В |

UOL, M |

0,5 |

Iоl =2,5 мА |

Выходное напряжение высокого уровня по выводам ШМК, В |

ион, м |

(3,5) |

Iон = 0,1 мА |

Выходное напряжение низкого уровня по выводу «Выбор кристалла», В |

UOL |

0,5 |

На выводе «Выбор кристалла» напряжение высокого уровня формируется извне |

Входное напряжение низкого уровня по входу R, В |

UiL |

0,8 |

— |

Входное напряжение высокого уровня по входу R, В |

ViH |

(2,4) |

|

Используются следующие форматы микрокоманд:

1. При микрокомандах арифметических, логических, регистровых, инкремента/декремента, сдвига, проверки и установки условий код операции содержится в разрядах 15—8 микрокоманды, разряды 7—4 микрокоманды содержат адрес регистра одного из операндов (порт

В блока РОН), а разряды 3 — 0 — адрес регистра другого операнда (порт А блока РОН).

При литеральных микрокомандах код операции содержится в разрядах 15 — 12 микрокоманды, адрес регистра операнда заключен в разрядах 3 — 0 (порт А блока РОН), а код литерала—в разрядах II—4 микрокоманды.

При микрокомандах ввода, вывода код операции содержится в разрядах 15—8 микрокоманды, разряды 3-0 содержат адрес регистра по порту А блока РОН, а в разрядах 7 — 4 микрокоманды заключена служебная информация, используемая для формирования соответствующих нанокоманд.

При микрокомандах перехода и передачи управления код операции содержится в разрядах 15 — 8 микрокоманды, а разряды 7 — 0 определяют адрес перехода.

Электрические статические параметры микросхем KH1811ВУ1, КН1811ВУ2, КН1811ВУЗ приведены в табл. 2, динамические -в табл. 3.

Таблица 3

Параметр |

Обозначение |

Значение параметров |

мин. |

макс |

Время установления сигналов нанокоманды, не |

tsu(NNS-C, LH) |

50 |

110 |

Время сохранения сигналов нанокоманды, не |

tH(NNS-C, HL) |

20 |

50 |

Время задержки сигнала микрокоманды, не |

td(MNS-C, HL) |

— |

110 |

Время установления сигналов команды, нc |

tSU(nS-C, LH) |

20 |

100 |

Время установления сигналов запросов прерываний, нc |

tSU(INTRQ-C, HL) |

20 |

100 |

Время сохранения сигналов команд, нc |

tH(NS — C, HL) |

20 |

50 |

Время сохранения сигналов запросов прерывания, нc |

tH(/NTRQ — C, LH) |

20 |

50 |

Время установления сигнала «Сброс», нc |

tSL:(RST.LH—CLH) |

20 |

100 |

Время сохранения сигнала «Сброс», нc |

th(RST-C, LH) |

20 |

50 |

Время задержки сигнала «Выбор кристалла», нc |

tD{CS, HL-C, LH) |

— |

110 |

|

tD(CS. LH-C, LH) |

|

|

|