Микросхема КР1802ИП1

Микросхема К.Р1802ИП1 — матрица многофункциональных ассоциативных регистров (MAP), предназначена для хранения данных, проведения контроля по четности, формирования признаков ассоциативного сравнения, восстановления исходной информации при сбоях в системах.

Микросхема может быть использована для построения на ее основе следующих видов быстрой памяти:

сверхоперативной (адресной) памяти с организацией «четыре плюс четыре регистра по пять разрядов»: (4+4) Х5 р;

сверхоперативной (адресной) памяти с организацией «четыре регистра по 10 разрядов»: 4ХЮ р;

ассоциативной памяти с поиском слова по равенству признака опроса (дескриптора) и ассоциативного признака, хранящегося в регистре, с возможностью маскирования разрядов сравниваемых чисел;

памяти с двухкоординатным поиском слова, т. е. выполнением ассоциативного сравнения в выбранной строке, с возможностью маскирования разрядов сравниваемых чисел;

специальных видов памяти типов СТЕК, КЭШ.

Устройства памяти, построенные с помощью микросхемы MAP, могут иметь любое число слов любой разрядности.

При построении ассоциативной памяти микросхема может работать как в поле ассоциативных признаков, так и п поле основной информации.

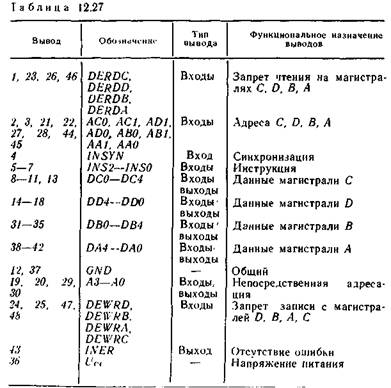

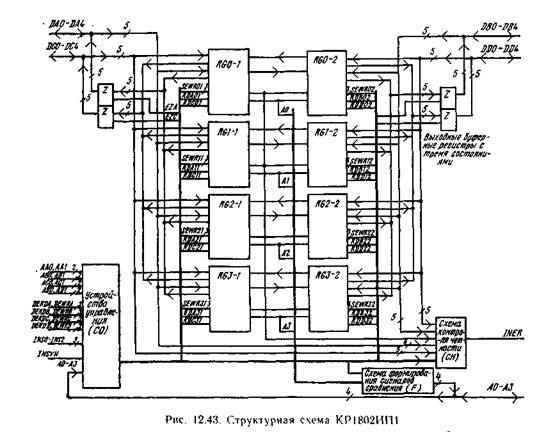

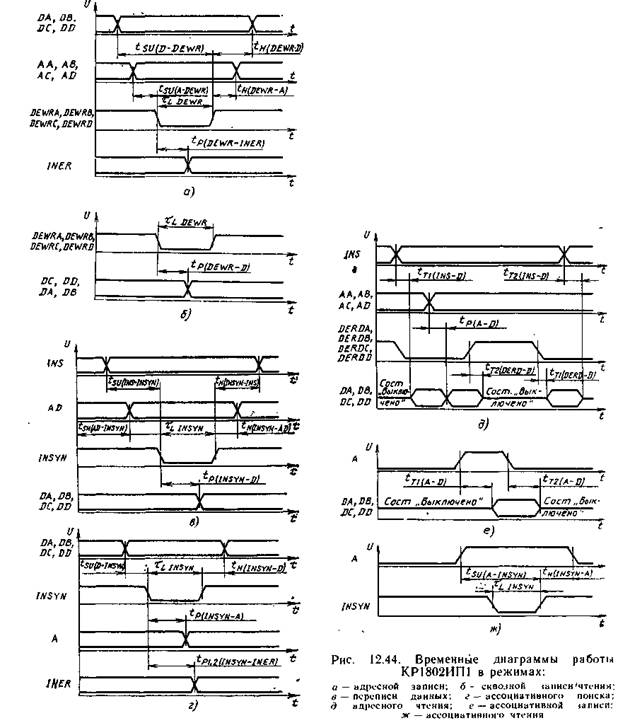

Условное графическое обозначение микросхемы приведено на рис. 12.42, назначение выводов - в табл. 12.27, структурная схема показана на рис. 12.43, временные диаграммы работы — на рис. 12.44.

Микросхема включает в себя следующие основные устройства: узлы матрицы ассоциативных регистров RG0-1, RG1-1, RG2-1, RG3-1, RGO-2, RG1-2, RG2-2, RG3-2; устройство управления СО; схему контроля четности СН; схему формирования сигналов сравнения F; выходные буферные регистры с тремя состояниями Z.

Узлы RG0-1—RG3-1 связаны с магистралями DAи DC; узлы RG0-2—RG3-2 — с магистралями DBи DD.

Входы/выходы DA4, DB4, DC4, DD4 предназначены для тетрадных контрольных разрядов.

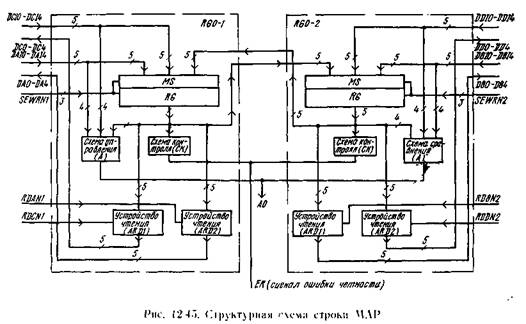

Структурная схема одной из строк микросхемы MAP, содержащая два узла MAP,- приведена на рис. 12.45. В состав узла MAP (RG) входят следующие устройства: мультиплексор MS, регистр RG, схема контроля СН, схема сравнения А, устройства чтения ARD.

На мультиплексор MSи регистр RGузла MAP подаются сигналы выбора данных и записи SEWR.

На соответствующую магистраль устройства чтения подаются сигналы чтения RDA, RDB, RDCили RDD.

Мультиплексор MSпо сигналам выбора и записи SEWRосуществляет передачу на вход регистра RGузла MAP информацию с входных шин DAIпли DCI(в левом столбце) и DB! или DDI(в правом столбце), а также информацию с выхода соседнего регистра данной строки. При этом каждый из трех сигналов SEWRразрешает прохождение информации с одного из направлений.

Регистр RGузла MAP является 5-разрядным регистром, построенным на D-трнггерах типа «защелка». Он производит запись и хранение информации, подаваемой на его вход с мультиплексора MS. Запись информации в регистр происходит при наличии сигнала высокого уровня на одном из входов SEWR.

Схема контроля СН узла MAP производит сложение по модулю 2 четырех разрядов данных и тетрадного контрольного разряда, хранящихся в регистре RGузла MAP. Наличие напряжения высокого уровня на выходе СН свидетельствует о возникновении ошибки четности информации в регистре RGузла MAP.

Выходы СН всех RGMAP объединяются для формирования общего сигнала ошибки четности хранимой информации ER.

Схема сравнения А обеспечивает сравнение внешнего признака опроса (дескриптора), поступающего по входной шине DAI (DBI), и ассоциативного признака, хранящегося в регистре. При этом сравниваемые числа могут быть замаскированы таким образом, что напряжение высокого уровня разряда маскн, поступающее по входной шине DCI (DD1), дает сигнал сравнения (напряжение высокого уровня) в данном разряде независимо от значений содержимого соответствующих разрядов регистрон и К скриптра онтрольные разряды четности в сравнении не участвуют.

Ассоциативное сравнение содержимого регистров и дескриптора происходит сразу во всей строке MAP. Поэтому выходы схем сравнения двух узлов MAP (одной строки) объединяются для формирования общего сигнала наличия сравнения в данной строке.

Устройство чтения ARDпо сигналам RDA (RDB) или RDC (RDD), поступающим из устройства управления, пропускает на соответствующую выходную шину DAO (DBO) или DCO (DDO) информацию с выхода регистра RGузла MAP

Устройство управления СО дешифрует адреса регистров узла MAP, к которым происходит обращение, и коды инструкций, задающих режимы работы микросхемы, осуществляет синхронизацию микросхемы, вырабатывает сигналы выбора данных и записи (SEWR) и чтения (RDA, RDB, RDC, RDD) для каждого узла MAP, а также сигналы разрешения включения 3-го состояния выходных буферных регистров Z, формирует признак наличия или отсутствия ассоциативного сравнения и данной схеме, управляет работой схемы контроля четности СН и схемы формирования сигналов сравнения F.

Схема СН проводит проверку на четность хранимой в регистрах информации во всех режимах работы, а также информации, находящейся на магистралях (т. е. дескриптора и маски), в режимах ассоциативного и двухкоординатного поисков. Наличие напряжения высокого уровня на выходе INERсвидетельствует об отсутствии ошибки четности в схеме.

В режимах ассоциативного и двухкоорди-натпого поисков на выход l\'ERможет подаваться также сигнал отсутствия сранненин в данной схеме (напряжение высокого уровни).

Схема формирования сигналов сравнения Fвырабатывает сигналы, свидетельствующие о наличии ассоциативного сравнения в одной илн нескольких строках микросхемы при ассоциативном или двухкоординатном поиске (в последнем случае адрес строки задается в Fс помощью сигналов из СО)-

Выходные буферные регистры с тремя состояниями обеспечивают возможность работы MAP с бннаправленными магистралями данных DA, DB, DC, DD, СО

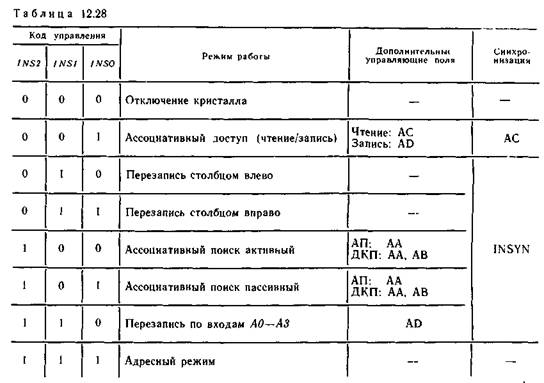

Режимы работы микросхемы MAP задаются с помощью входов инструкций INS2—INS0 и дополнительных сигналов управления. В качестве дополнительных сигналов управления используются сигналы, поступающие по адресным шинам АА, АВ, AC, AD.

Коды инструкций и соответствующие им режимы работы приведены в табл. 12.28 и 12 29.

Синхронизация режимов работы микросхемы осуществляется путем подачи следующих сигналов:

запрета записи DEWRA, DEWRB, DEWRC, DEWRDи запрета чтения DERDA, DERDB. DERDC, DERDDдля синхронизации адресного режима работы с магистралями DA, DB, DC, DDсоответственно;

АСО (ACt) для синхронизации режима ассоциативного чтения по объединенной магистрали DA—DB (DC—DD);

INSYNдля синхронизации остальных ассоциативных режимов и переписи информации.

Основным режимом работы микросхемы MAP является адресный (режим сверхоперативной памяти). При работе микросхемы в адресном режиме каждой магистрали соответствуют управляющие сигналы:

запрета чтения на данную магистраль (DERDA, DERDB, DERDC, DERDDдля магистралей DA, DB, DC, DDсоответственно);

запрета записи с данной магистрали (DEWRA, DEWRB, DEWRC, DEWRDдля магистралей DA, DB, DC, DDсоответственно);

двухразрядного адреса конкретного узла МАР-столбца, работающего с данной магистралью.

При этом магистралям DAи DCсоответствуют левый столбец узлов MAP (RG0-1— RG3-1) и адресные поля АА и АС соответственно, а магистралям DBи DD— правый столбец (RGQ-2—RG3-2) и адресные поля АВ и ADсоответственно.

Адресация регистров узлов MAP с помощью адресных полей производится согласно табл. 12.30.

При работе микросхемы в режиме сверхоперативной (адресной) памяти с организацией «четыре плюс четыре регистра по пять разрядов» управление чтением и записью относительно любой из магистралей производится независимо и одновременно. Это позволяет в один и тот же момент осуществить чтение любого регистра столбца на любую из двух соответствующих магистралей и запись информации в любой регистр столбца с любой из двух соответствующих магистралей.

Одновременное чтение информации из нескольких регистров на одну и ту же магистраль и запись информации в несколько регистров с одной и той же магистрали невозможны.

В режиме сверхоперативной памяти с организацией «четыре регистра по десять разрядов» микросхема MAP рассматривается как четыре байтовых регистра, имеющих по два тетрадных контрольных разряда.

Один байтовый регистр образует два регистра RGодной строки. Регистры подключены к двум 10-разрядным (с линиями контрольных разрядов) бинаправленным магистралям. Данная структура получается путем объединения по управлению магистралей DAс DBи DCс DD. Управление чтением/записью по каждой из полученных магистралей независимое, с использованием полей признаков чтения/записи (полей DERDA—DERDDи DEWRA—DEWRD) и адресных полей АА, АВ, AC, AD. В дальнейшем, если линии контрольных разрядов не участвуют в функциональном описании, объединенные магистрали называются байтовыми магистралями DA—DBи DC—DD.

Адресный режим может использоваться одновременно и независимо с любым другим ре жимом; ирн этом в адресном режиме могут использоваться только те адресные поля, которые не задействованы в данном режиме работы в качестве дополнительных.

Обмен информацией в адресном режиме при совмещении с При подаче на несколько входов непосредственной адресации напряжения высокого уровня происходит одновременный выбор нескольких соответствующих строк. Данная ситуация допустима в режиме ассоциативной записи (производится запись одинаковой информации в несколько строк матрицы:, но недопустима в режиме ассоциативного чтения, так как в этом случае информация на магистралях будет неопределенной.

Управление чтением (записью) производится с помощью позиционного кодирования в полях АС и AD(см. табл. 12.29).

Синхронизация ассоциативной записи производится с помощью сигнала INSYNнизкого уровня, а ассоциативного чтения — непосредственно сигналами ACQ, ACI. Данный режим используется при работе микросхемы в поле основной информации ассоциативной памяти, а также при необходимости осуществить чтение или запись информации по сигналам непосредственной адресации в адресной памяти.

При подаче кода INS2 1NS1=01 задается режим переписи столбцом. При этом при подаче синхронизирующего сигнала INSYNнизкого уровня происходит перепись инфopмaции во всех строках одновременно в направлении, указанном с помощью разряда INS0 (см табл. 12.28). Значение INS0 = 0 задает перепись влево, т. е. из регистров RG0-2—RG3-2 е регистры RG0-1—RG3-1 соответственно, значение lNSl = \ задает перепись вправо, т. е. из регистров RG0-1—RG3-1 в регистры RG0-2— RG3-2 соответственно.

Направление переписи может быть заданс жестко (INS0 задается вместе с INS2, INS1) либо вычислено в ходе преобразований и отображено значением INS0. Данная возможность может быть использована при организации вычислений по альтернативным ветвям. Так как дополнительных управляющих полей нет, режим переписи столбцом можно задавать совместно с адресным режимом в одной микрокоманде без какой-либо последующей коммутации управляющих потоков. Указанная особенность является важной для простой и эффективной реализации процедур восстановления вычислительного процесса.

При работе микросхемы в режиме ассоциативного поиска (INS2 INS1 = \0) содержимое четырех байтных регистров, предназначенных в данном случае для хранения ассоциативных признаков информации соответствующих ячеек поля памяти, сравнивается с внешним признаком (дескриптором), подаваемым по байтовой магистрали DA—DB. Контрольные разряды в сравнении не участвуют.

Разряды сравниваемых чисел могут быть замаскированы содержимым магистрали DC— DDтак, что единичное значение разряда маски дает сравнение в данном разряде независимо от значений соответствующих разрядов ассоциативного признака и дескриптора.

Режим ассоциативного поиска в микросхеме MAP задается кодом INS2 INS1 = 10. Значение INS0 определяет, является режим поиска активным (INS0 = 0) либо пассивным (1NS0=\). Режим активного поиска предполагает выдачу по выходам непосредственной адресации АО—A3 результатов поиска (AN=1 — есть сравнение в соответствующей строке). Результаты сравнения по каждому байтовому ассоциативному признаку выдаются микросхемой для активизации режимов чтения или записи в соответствующих ячейках поля основной памяти (на входы непосредственной адресации в случае использования в иих также микросхемы MAP). Выходы непосредственной адресации выполнены с открытым коллектором, что позволяет расширить по горизонтали поле ассоциативных признаков до необходимых размеров. При этом несовпадение частей дескриптора и ассоциативного признака хотя бы в одной микросхеме горизонтального ряда дает общий сигнал отсутствия сравнения дескриптора и признака.

Синхронизация выдачи сигналов непосредственной адресации производится с помощью сигнала INSYNнизкого уровня. Кроме описанного простого ассоциативного поиска микросхема MAP может производить двухкоординатиый поиск информации. В этом случае сигнал непосредственной адресации будет выдан только в одной, выбранной с помощью кода в адресном поле АВ (АВ1, АВО), строке при условии, что ассоциативный признак, хранящийся в данной строке, равен дескриптору.

Маскирование двухкоординатного сравнения производится так же, как и при простом ассоциативном поиске. Вид поиска задается значением АА1 : АА1 = 0 — простой ассоциативный поиск; АА1 = \ — двухкоординатный поиск.

Двухкоординатный поиск может быть применен и в том случае, когда в поле ассоциативных признаков сравнение признака и дескриптора произошло не в одной, а в нескольких строках одновременно. При этом возникает необходимость выбора одной из них. Конкретный вид алгоритма выбора строки с помощью двухкоординатного поиска определяется разработчиком ассоциативной памяти.

Загрузка ассоциативных признаков в регистре микросхемы MAP может производиться либо в режимах сверхоперативной памяти, либо в режиме ассоциативной памяти с использованием аппарата непосредственной адресации (в режиме ассоциативного доступа).

В пассивном режиме по выходам непосредственной адресации подается сигнал отсутствия сравнения (все AN = Q). Таким образом, вход INS0 при INS2 INS1 = \0 может быть использован для активизации режима поиска в части памяти заданной конфигурации; при этом значения дополнительных управляющих полей могут быть любыми.

Режим построчной переписи задается значением кода INS2 INSIINS0=UQ.

Выбор конкретной строки, в которой должна быть произведена перепись информации, осуществляется заданием активного (высокого) уровня сигнала на соответствующем входе непосредственной адресации (см. табл. 12.31)* Направление переписи (влево/вправо) определяется полем AD(см. табл. 12.29). Комбинация AD1 AD0=00 является запрещенной, так как результат переписи при этом непредсказуем.

Режим построчной переписи синхронизируется сигналом INSYN.

При подаче кода /NS2 INS1 INS0=1Uединственно возможным режимом работы является адресный. Никакая другая информация, относящаяся к другим режимам, не воспринимается. Выходы непосредственной адресации АО—A3 выключаются (AN=I).

При работе микросхемы MAP во всех режимах необходимо принимать меры но уст ранению возможного одновременного обращения по записи к одному и тому же регистру с нескольких направлений, поскольку сигналы выбора и записи SEWRвырабатываются устройством управления независимо друг от друга. Анализ указанной конфликтной ситуации в микросхеме ие проводится.

Достоверность хранимой в микросхеме информации непрерывно контролируется с помощью проверки на четность информационных и контрольных разрядов. Если информация правильная, то сумма по модулю 2 разрядов тетрады и соответствующего контрольного разряда равна нулю.

В любом режиме при появлении ошибки в любом из регистров на входе INERпоявляется общий нестробированный сигнал ошибки (INER = 0 — есть ошибка информации в данной микросхеме). Выход выполнен с открытым коллектором, что позволяет наращивать память с контролем на микросхеме MAP до необходимых размеров.

В соответствии с конкретными задачами по локализации ошибки объединение выходов INERможно производить различными способами:

объединять выходы INERвсех микросхем, принадлежащих к одному горизонтальному ряду участка памяти;

объединять выходы INERвсех микросхем, принадлежащих к данному участку памяти.

При этом возникновение ошибки хотя бы одной из микросхем горизонтального ряда (участка памяти) приведет к формированию сигнала ошибки для всего данного ряда (участка памяти).

Если не проводить объединения выходов INER, то можно определить конкретную микросхему, в которой произошла ошибка информации, однако это может привести к значительному усложнению схемы анализа ошибок.

В режиме ассоциативного поиска (INS2 INSI=\0) на выход INERможет подаваться дополнительная информация, которая определяется сигналами на входах INSYNи ААО. При активном (низком) уровне сигнала INSYNи АА0=0 иа выход INERподается общая информация об ошибках в регистрах и на магистралях (INER —0 соответствует наличию ошибки), т. е. в данном случае дополнительно производится контроль по четности информации, находящейся на магистралях (дескриптора и маски).

При активном (низком) уровне сигнала INSYNи АА0=! на выход INERподается информация о наличии сравнения ассоциативного признака и дескриптора хотя бы в одной строке данной микросхемы (INER = Q— есть сравнение). В режиме пассивного поиска при низком уровне сигнала на входе при INSYN = 0 и АА0=1 на выход INERподается сигнал отсутствия сравнения (INER=1).

При пассивном (высоком) уровне сигнала на входе INSYNв режимах ассоциативного поиска на выход INERподается информация об ошибках по четности хранимых в регистрах данных.

В ассоциативном режиме аппарат управления микросхемой MAP позволяет выполнить следующее:

ассоциативное чтение. В этом режиме из непосредственно адресуемого регистра (по входам АО—A3) на любую из магистралей (DA—DB, DC—DD) читается информация, ас соцнативный признак которой совпадает с дескриптором; при этом сравниваемые числа могут быть замаскированы. Сравнение с дескриптором происходит в микросхемах MAP, хранящих ассоциативные признаки;

ассоциативная запись.

Информация с одной из магистралей заносится в непосредственно адресуемый регистр, ассоциативный адрес которого равен дескриптору (с учетом маскирования).

Сравнение происходит в микросхемах MAP, хранящих ассоциативные признаки;

смешанный режим ассоциативного чтения/записи;

смешанные адресный и ассоциативный режимы чтения/записи (с учетом адресной совместимости).

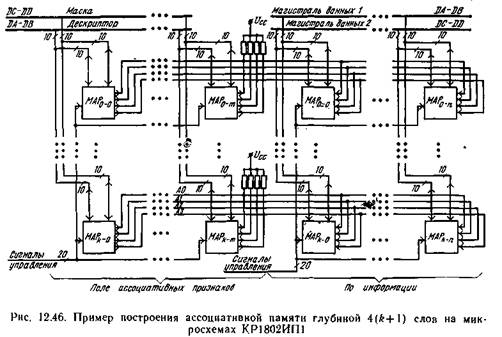

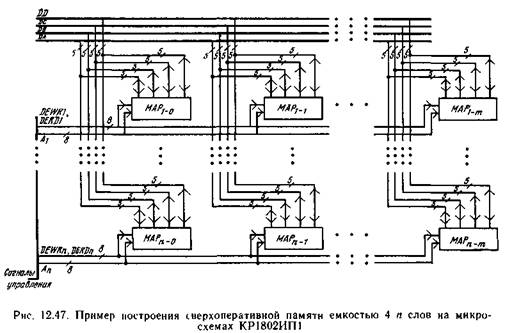

Пример построения ассоциативной памяти глубиной 4 (Л-f-1) слов с (т+1 (-байтовым полем признака и (и+1)-байтовым полем основной информации показан на рис. 12.46. Пример построения адресной сверхоперативной памяти емкостью 4 п слов на микросхеме MAP показан на рис. 12.47. В приведенном примере при одинаковом управлении всеми микросхемами по парам магистралей DA—DBи DC—DDполучается двухвходовая (двухадресная) память, каждый байт которой имеет выход на любую из двух бинаправленных байтовых магистралей, в совокупности составляющих полноразрядные (т+1)-байтовые магистрали данных DA—DBи DC—DD. При независимом управлении микросхемами

MAP по каждой из магистралей DA, DS, DC, DDполучаются две (т+1)/2-байтовые двухвходовые памяти с возможностью переписи информации внутри строк из одной памяти в другую.

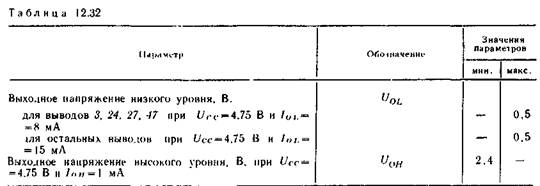

Основные параметры микросхемы

КР1802ИП1 поиведены в табл. 12.32.

|