Микросхема КР1802ИР1

Микросхема КР1802ИР1 — двухадресный регистр общего назначения (РОЙ) на 64 бита, предназначена для реализации сверхоперативных запоминающих устройств процессоров и многоадресных оперативных запоминающих устройств радиоэлектронной аппаратуры.

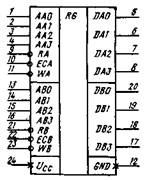

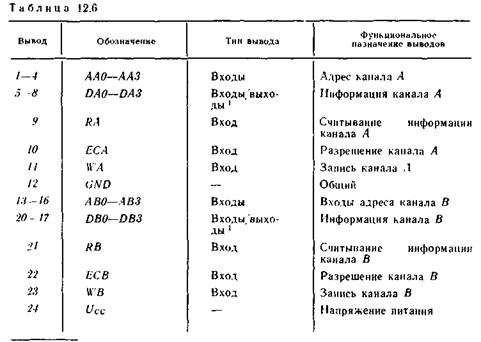

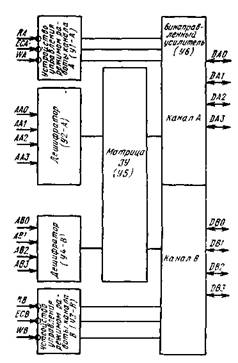

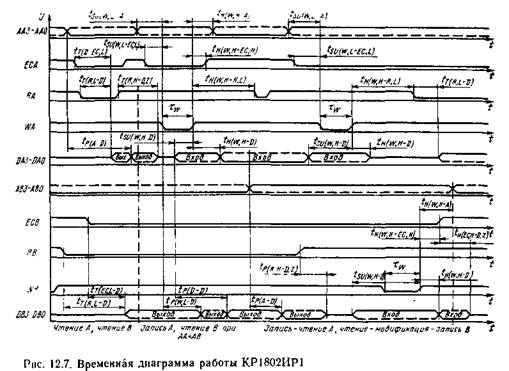

Условное графическое изображение микросхемы приведено на рис. 12.5, назначение выводов — в табл. 12.6, структурная схема показана на рис. 12.6, временная диаграмма работы — на рис. 12.7.

Микросхема состоит из матрицы 16X4 бит (У5), включающей 16 4-разрядных регисгро и, дешифраторов (У2-А) и (У4-В) выбора необходимого регистра по каналам А и В соответственно, двух устройств управления режимом работы (У1-А) и (УЗ-В) каналами А и В соответственно, биполярного усилителя (У6), состоящего нз восьми усилителей считывания с тремя устойчивыми состояниями на выходе и восьми усилителей записи.

Усилитель считывания и записи каждого разряда матрицы работает на один разряд соответствующего канала.

|

Рис. 12.5 |

|

Рис 12.6 |

|

Разрешением обмена информацией матрицы РОН с каналами Л и В управляют входы ЕСА и ЕСВ. При наличии лог. О на входе ЕСА разрешен обмен информацией с каналом А. При наличии лог. О иа входе ЕСВ разрешен обмен информацией с каналом В. При наличии лог. О на входах ЕСА и ЕСВ обмен информацией с матрицей РОН разрешен по обоим каналам.

Входы RA и RB определяют режим считывания информации из матрицы БИС РОН на каналы А или В. При наличии лог. О на входе RA разрешено считывание на канал А. При наличии лог. О на входе RB разрешено считывание на канал В. При наличии лог. О на входах RA и RB считывание разрешено одновременно на каналы А и В.

Входы WA и WB определяют режим записи информации в матрицу РОН с каналов А и В. При наличии лог. О на входе WA запись информации разрешена с канала А; при этом выход усилителя считывания канала А должен быть закрыт (3-е состояние). На входе RA должно быть напряжение лог. 1.

При наличии лог. О на входе WB запись информации разрешена с канала В; при этом выход усилителя считывания канала В должен быть закрыт. На входе RB должно быть напряжение лог. 1.

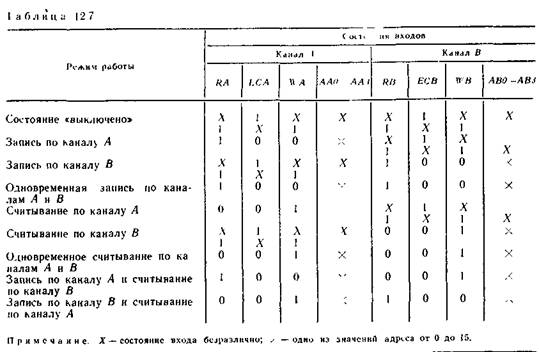

При наличии лог. О на входах WA, WB запись информации разрешена с обоих каналов. Режимы работы РОН приведены в табл. 12.7.

Выборка необходимого регистра матрицы РОН как в режиме записи с канала А или В, так и в режиме считывания на канал А или В осуществляется двумя дешифраторами методом задания двоичного кода на входы адреса: ААО—ААЗ — для канала А; АВО—АВЗ— для канала В.

Матрица РОН состоит из триггерных ячеек с организацией 16X4.

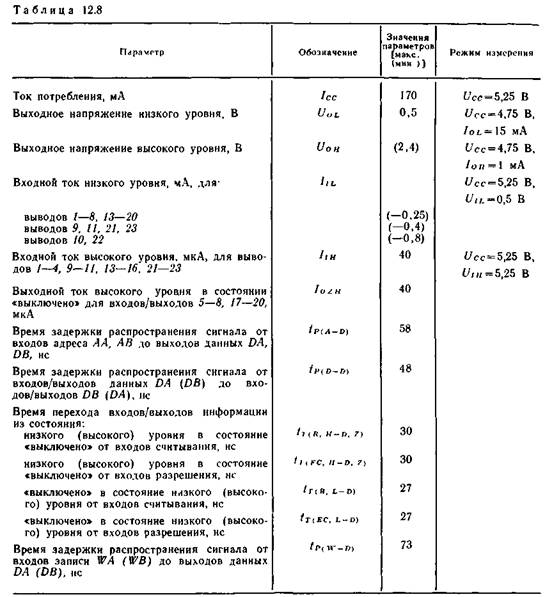

Основные параметры микросхемы

КР1802ИР1 приведены в табл. 12.8. |