Микросхема КР1802ВС1

Микросхема КР1802ВС1 микропроцессорной секции (МС) — 8-разрядная наращиваемая секция устройства обработки данных, предназначена для выполнения следующих операций:

арифметическое сложение и вычитание в дополнительном коде;

логические операции конъюнкции, дизъюнкции, инверсии и сложение по модулю 2;

арифметические, логические и циклические сдвиги вправо и влево на один разряд.

При выполнении перечисленных операций возможно производить многочисленные операции маскирования содержимым регистра расширения отдельных разрядов входных данных.

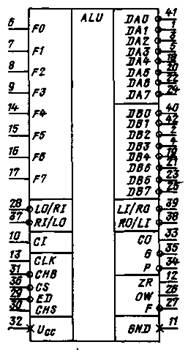

По результату операции вырабатываются признаки равенства 0 результата и признак переполнения (в операциях сложения, вычитания, сдвига влево). При соединении нескольких микросхем МС можно производить последовательный и ускоренный перенос, операции обработки байтов, широкий набор операций сдвигов, включая и расширенные сдвиги, т. е. сдвиг двойного слова совместно с регистром расширения без внешних дополнительных схем с выработкой признаков результата только в выбранных кристаллах. Условное графическое обозначение микросхемы приведено на рис. 1, назначение выводов — в табл.1, структурная схема по казана на рис..2.

Рис. 1

Таблица 1

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

41, 1, 3, 5, 18, 20, 22, 24 |

DA0—DA7 |

Входы/выходы |

Информация |

40, 42,2,

4, 19,21,

23, 25 |

DB0—DB7 |

Входы/выходы |

Информация |

6-9, |

F0—F7 |

Входы |

Код микрокоманды |

14—17 |

|

|

|

28 |

LO/RI |

Выход/вход |

Сдвиг влево/вправо САЛУ |

37 |

RI/LO |

Вход/выход |

Сдвиг вправо/влево СРР |

39 |

LI/RO |

В,ход/выход |

Сдвиг влево/вправо САЛУ или перенос из 3-го разряда АЛУ |

38 |

RO/LI |

Выход/вход |

Сдвиг вправо/влево СРР |

10 |

CI |

Вход |

Перенос |

33 |

СО |

Выход |

Перенос |

13 |

CLK |

Вход |

Синхронизация |

31 |

СНВ |

Вход |

Управление инверсией старшего разряда |

36 |

CS |

Вход |

Выборка кристалла |

29 |

ED |

Вход |

Разрешение выдачи информации |

30 |

CHS |

Вход |

Выборка старшего кристалла |

35 |

G |

Выход |

Генерация переноса |

34 |

P |

Выход |

Распространение переноса |

12 |

ZR |

Выход |

Признак равенства 0 результата |

26 |

OW |

Выход |

Признак переполнения |

27 |

F |

Выход |

Выдвигаемые разряды АЛУ или выходной перенос СО |

32 |

Ucc |

— |

Напряжение питания +5 В |

11 |

GND |

— |

Общий |

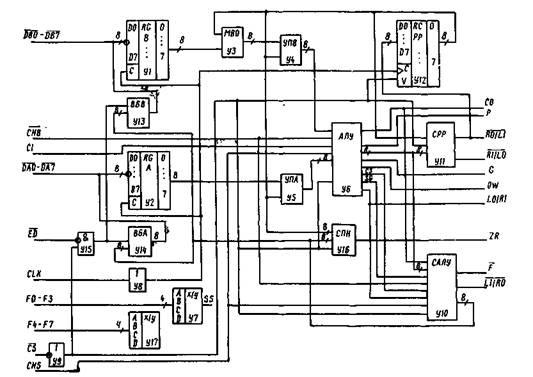

В состав микросхемы входят следующие основные узлы: У1 — регистр данных В (РВ); У2 — регистр данных А (РА); УЗ — мультиплексор выбора операнда (МВО); У4 — узел подготовки данных В (УПВ); У5 — узел подготовки данных А (УПА); У6 — арифметико-логическое устройство (АЛУ); У7 — дешифратор микрофункций операции; У8 — буферная схема сигнала синхронизации; У9 — буферная схема сигнала выбора микросхемы; УЮ — сдвигатель арифметико-логического устройства (САЛУ); У11 — сдвигатель регистра расширения (СРР); У12 — регистр расширения (РР); У13 — выходной буферный каскад В (ВБВ); У14 — выходной буферный каскад А (ВБА); У15 — вентиль стробирующего сигнала выдачи данных; У16 — схема признака нуля (СПН); У17 — дешифратор микрофункций модификации.

Рис. 2

При описании МС используются следующие условные обозначения: L0—L7 — информация на выходах АЛУ; R0—R7 — информация на выходах САЛУ; SG — сигнал из АЛУ, образующийся из старших разрядов РА, РВ; МО—М7 — информация на первом входе АЛУ; К0—К7 — информация на втором входе АЛУ; 55 — признак операции вычитания в АЛУ.

Разряды А7, В7, L7, R7 — старшие разряды информации.

Разряды микроинструкции F0—F3 определяют операцию АЛУ с данными, поступающими из РА и МВО. Эти операции перечислены в табл. 12.3. Разряды микроинструкции F4— F7 определяют операции модификаций МС (табл. 12.4). К этим операциям относятся.

выбор операнда в МВО, т. е. операция с РВ или РР;

разрешение операции маскирования;

различные операции сдвигов.

Выражение L — f(A, В, Р) определяет одну из операций АЛУ при наличии маскирования данных из РА и РВ содержимым PP. операции АЛУ при L = f(A, В, Р) представлены в колонке L = f(A, В, Р) табл. 12.3.

В колонке «R7—R0 — результат операции САЛУ» (см. табл. 12.4) показан результат операции сдвига. Эта информация при CS Л Д??>=1 выдается на магистрали DA7— DAO, DB7—DB0 В колонках Ll/RO, LO/RI, ROjLl, R1/LO табл. 12.4 показана информация, появляющаяся на этих выводах при различных кодах на шинах F4—F7, CS, CHB. Если в соответствующих строках этих колонок стоит знак <rZ», то это означает, что выход схемы находится в 3-м (высокоомном) состоянии.

В операциях, где нет сдвига, на вывод LIIRO выдается значение выходного переноса из 3-го разряда АЛУ (СЗ).

Во всех случаях, если кристалл не выбран (С5 = 0), при сдвигах влево происходит сквозное распространение информации через СРР и САЛУ с вывода LI/RO на LO/RI и с вывода RO/LI на R1/L0, а при сдвигах вправо — переход информации с вывода RI/LO на RO/LI и с вывода LO/RI на LI/RO.

В колонках признаков F, OW и ZR показаны значения признаков, которые вырабатываются при различных операциях. Все выводы признаков — с открытым коллектором. Если CS=0, то при подключении внешнего резистора на этих выводах будет напряжение высокого уровня, что позволит использовать монтажное объединение.

Если кристалл выдраи, то в СПН анализируется результат САЛУ. И если разрешено маскирование (код на шине F4, F5, F6, F7= = 1111), результат САЛУ маскируется разрядами РР, равными 0. Если все разряды маскированного результата равны 0, то на выводе ZR — напряжение высокого уровня. Если операция без маскирования, то на равенство 0 анализируются все разряды САЛУ.

На вывод F в модификациях без сдвига (если АЛУ выполняет операцию арифметического сложения) выдается значение переноса в прямом коде. Управляет инверсией выходного переноса внутренний признак 55, который равен 1 при вычитании и 0 при сложении и логических операциях.

При операции сдвига на выход F выдается значение выдвигаемого разряда в обратном коде.

В колонках LI/RO, LO/RI, R1JLO, RO/L1 табл. 12.4 записаны логические условия образования соответствующих сигналов. Формирование сигналов G, СО и Р АЛУ зависит от значения управления на шине CS. Если кристалл выбран (на шине напряжение низкого уровня), то на шину СО поступает значение выходного переноса из старшего разряда в прямом коде. Если кристалл не выбран, то происходит передача переноса со входа С/ на выход СО и устанавливается G = l, Р=0 для обеспечения распространения входного переноса через схему ускоренного переноса В АЛУ вырабатывается также перенос из младшей тетрады. Значение этого переноса выдается в операциях модификации без сдвига по выходу LI/RO и может быть использовано для организации внешнего корректора при реализации операции десятичной арифметики. |