3. Микросхема К589ИК01

Микросхема К589ИК01 - блок микропрограммного управления (БМУ), предназначен для использования в устройствах микропрограммного управления. Она выполняет следующие операции:

- прием начального адреса микропрограмм по 8-разрядной шине данных;

- управление последовательностью выбора микрокоманд из памяти микропрограмм;

- хранение и анализ 4-разрядного кода команды на регистре команд;

- выдача трех разрядов регистра команд для адресации регистров в ЦПЭ;

- хранение двух признаков и условный переход по ним;

- управление прерываниями микропрограммного уровня;

- выдача на вход ЦПЭ или других устройств признаков, лог. 1 и лог. 0;

- непосредственная адресация стандартных биполярных ПЗУ и ППЗУ;

- адресация 512 микрокоманд с возможностью увеличения числа адресации ячеек дополнительными схемами.

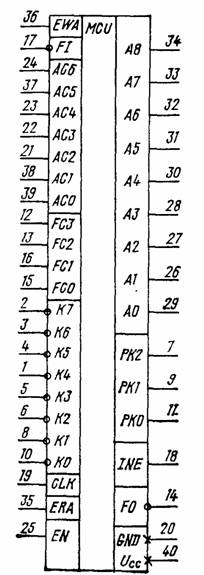

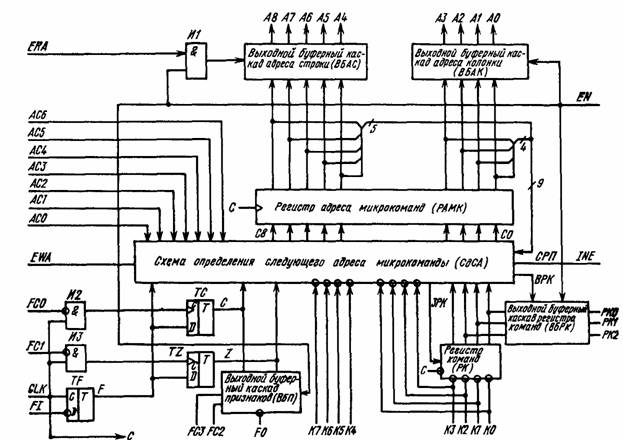

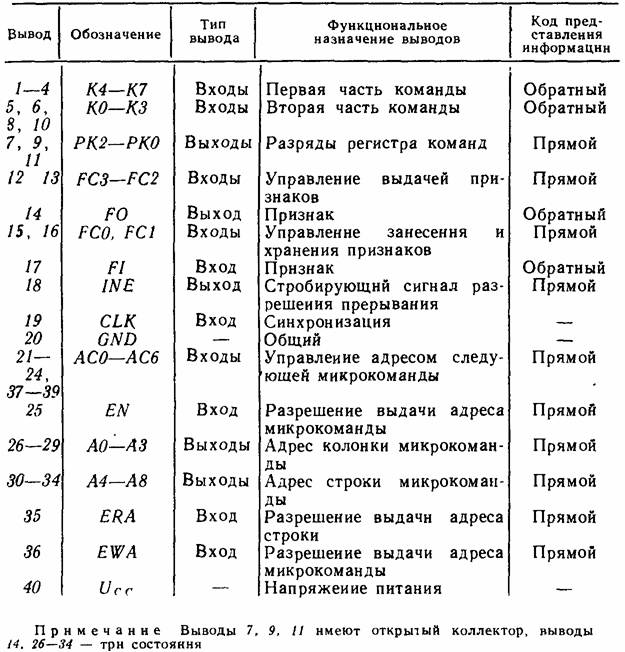

Условное графическое обозначение микросхемы приведено на рис. 7, назначение выводов— в табл. 9, структурная схема показана на рис. 8.

рис.7

рис.8

таблица 9

В состав БМУ входят следующие основные узлы:

РАМК — регистр адреса микрокоманд; СОСА — схема определения следующего адреса микрокоманды; РК—регистр команд; ВБАС - выходной буферный каскад адреса строки; ВБРК— выходной буферный каскад регистра команд; TF - триггер F; ТС — триггер С; TZ — триггер Z; ВВП—выходной буферный каскад признаков; И1, И2, ИЗ — логические элементы И; ВБАК — выходной буферный каскад адреса колонки.

При описании структурной схемы используются следующие условные обозначения внутренних сигналов:

F— содержимое TF; С — содержимое ТС; Z— содержимое TZ; ЗРК— сигнал разрешения записи в РК: ВРК — сигнал разрешения выдачи содержимого РК; С8—С0 — адрес следующей микрокоманды, поступающей на входы РАМК; РК2—РК0 — содержимое РК;

РАМК - 9-разрядный регистр адреса микрокоманд, состоящий из D-триггеров с записью информации по фронту сигнала синхронизации С. На входы DРАМК с выходов COCA поступает информация, которая является адресом следующей микрокоманды. Информация с выходов РАМК поступает на ВБАС, ВБАК и COCA;

COCA - комбинационная схема, которая в зависимости от значений управляющих сигналов на входах АСО - АС6, EWAи информации, поступающей с шин КО - К7 и узлов TF, ТС, TZ, РАМК и РК, формирует сигналы: С8 - С0, СРП - сигнал разрешения прерывания, ЗРК, ВРК.

РК - 4-разрядиый регистр команд, состоящий из D-триггеров типа «защелка>, записывающих информацию со входов КЗ - К0 при ЗРК=1 н С=0. РК используется для хранения разрядов команды, по которым в дальнейшем можно выполнить условный переход, или при выдаче содержимого РК на выходы РК0 - РК2 для определения адреса регистра в ЦПЭ;

ВБАС - служит для выдачи старших разрядов РАМК на выходы А4 - А8, которые определяют адрес строки следующей микрокоманды. Выходы А4 - А8 переводятся в 3-е (высокоомное) состояние при ЕЯА = 0 или EN - 0; если ERA =1 и EN=1, то на выходы А4 - А8 передается информация со старших разрядов РАМК;

ВБАК - служит для выдачи младших разрядов РАМК на выходы A3 - АО, которые определяют адрес колонки следующей микрокоманды. Выходы A3 - АО переводятся в 3-е состояние при EN - 0; если ЕN=1, то на выходы A3 - АО передается информация о младших разрядах РАМК;

ВБРК - служит для выдачи трех младших разрядов РК на выходы РКО—РК2.

Выдача информации происходит при EN=1 и ВРК=1; в противном случае на выходах РК0 - РК2 - напряжение высокого уровня.

TF - D -триггер типа «защелка> служит для хранения при С = 0 инвертированной информации со входа FI. Информация Fс выхода TFиспользуется при условных переходах в COCA и поступает на D— входы ТС и TZ. При CLK= 1 TFотслеживает значение иа выходе F1, причем F=F1;

ТС - D-триггер с записью информации по фронту. Запись в ТС происходит при £С0=О по фронту сигнала синхронизации. Содержимое ТС используется в COCA при условных переходах или может быть передано на выход FOпри FC3=Qи £С2=1; при этом £0 = С;

TZ - D-триггер с записью информации по фронту. Запись в TZпроисходит при £С/=0 по фронту сигнала С. Содержимое TZиспользуется в COCA при условных переходах или может быть передано на выход FOпри FC3= = !, £С2 = 0; при этом FO = 2;

ВБП - служит для выдачи на выход F0 содержимого TC, TZлог. 1 или лог. О при EN=1. Если EN=0, то

ыход F0 — в 3-м состоянии. Выборка следующего адреса микрокоманды БМУ обеспечивает выполнение функции безусловных и условных переходов. Эти функции используются для реализации операций безусловного и условного переходов в составе каждой микрокоманды. Каждая микрокоманда обычно содержит поле операции перехода, которое определяет команду перехода и, следовательно, следующий адрес микрокоманды.

Для минимизации числа выводов БМУ и упрощения логической схемы выборки следующего адреса массив адресов микропрограмм организован в виде двумерного массива (матрицы). Каждый адрес микрокоманды соответствует элементу матрицы на пересечении определенных строки и колонки. Таким образом, 9-разрядный адрес микрокоманд определяется двумя адресами: адресом строки (старшие пять разрядов) и адресом колонки (младшие четыре разряда). Следовательно, матрица адресов может содержать максимально 32 адреса строки и 16 адресов колонок — всего 512 адресов.

Логическая схема выборки следующего адреса БМУ широко использует эту двумерную схему адресации. Например, из любого места матрицы, определенного своей строкой и колонкой, можно безусловно передавать управление в любое место адресной матрицы. Действительно, для каждого данного адреса (элемента матрицы) существует фиксированное подмножество адресов микрокоманд, которые могут быть выбраны в качестве следующего адреса. Эти адреса, на которые возможен переход, назовем множеством перехода. Каждый тип функции перехода БМУ обладает своим множеством переходов.

Логическая схема признаков БМУ обеспечивает хранение текущего значения признака, поступающего на вход F1, и выдачу его на выход признаков F0. Функции переходов БМУ выбираются в зависимости от сигналов на семи входных шинах, обозначенных АС0—АС6. По фронту синхросигнала 9-разрядиый адрес микрокоманд, выработанный логической схемой определения следующего адреса, загружается в регистр адреса микрокоманд. Этот адрес микрокоманды из РАМК выдается в память микрокоманд по девяти выходным шинам, обозначенным А0 - А8. Выходы адреса микрокоманд подразделяются на выходы адресов строк и колонок следующим образом: А8 - А4 - адрес строки; A3—А0 - адрес колонки.

Каждой функции управления адресом соответствует своя кодовая комбинация на функциональных входных шинах АС. Разряды 2—6 этой кодовой комбинации определяют вид функции. Ниже следует детальное описание каждой из 11 функций переходов. Для указания адресов строк и колонок используются следующие обозначения: СТРn — 5-разрядиый адрес следующей строки; КОЛn — 4-разрядный адрес следующей колонки; п — десятичный номер строки или колонки. Для выработки следующего адреса микрокоманды по безусловному переходу используется текущий адрес микрокоманды, т. е. содержимое регистра адреса микрокоманд перед приходом синхроимпульса, и некоторые разряды из кода на шинах АС.

Таким образом, последующая функция перехода будет использовать адрес строки в регистре РАМК, а не измененный адрес строки. Заметим, что функция загрузки всегда блокирует функции переходов на шинах АСО—АС6. Однако по ней не блокируется разрешение на выдачу содержимого РК на шины РКО—РК2, а также разрешение на прием в РК содержимого шин К4—К7 при наличии на шинах функции ICEи JPXсоответственно. Кроме того, по шине EWAне запрещается разрешение строба прерывания и всех функций управления признаками. При подаче лог. 0 на вход ENвыполнение функции БМУ не блокируется, но выходы А0—А8, F0 и РК2—РК0 переводятся в 3-е состояние.

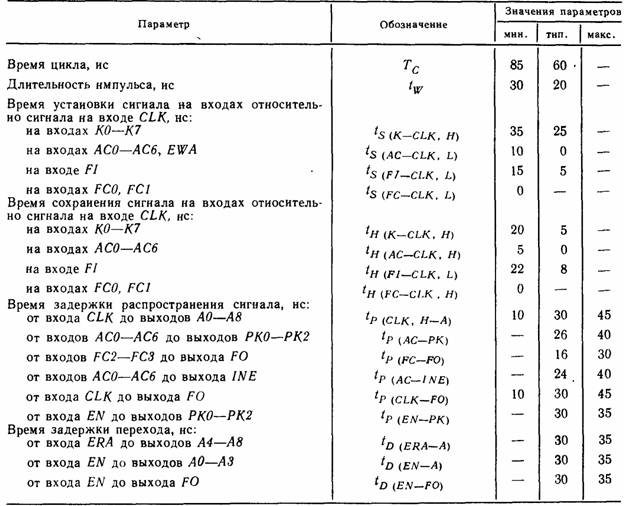

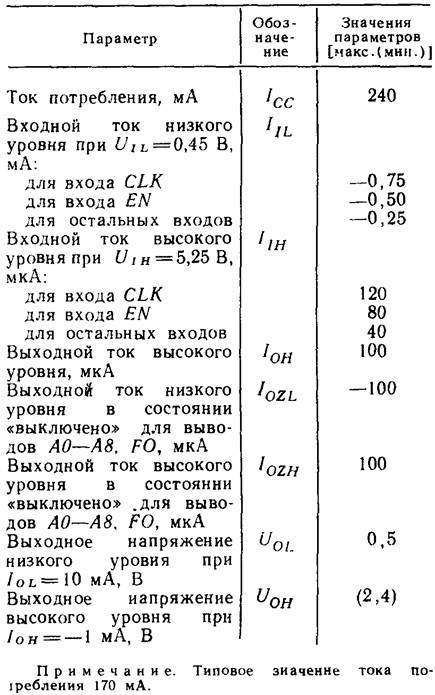

В табл. 10 и 11 приведены статические и динамические параметры К589ИК01.

Таблица 10

Таблица 11

|