Микросхема К589ИР12

Микросхема К589ИР12 — миогорежимиый буферный регистр (МБР), является универсальным 8-разрядиым регистром с выходами, имеющими три состояния. Он имеет встроенную логическую схему и независимый триггер для формирования запроса на прерывание центрального процессора. Одни или несколько МБР могут использоваться для реализации многих типов интерфейсных и вспомогательных устройств, включая: простые регистры данных; буферные регистры со стробированием данных; мультиплексоры; двунаправленные шиииые формирователи; прерываемые каналы ввода/вывода и др.

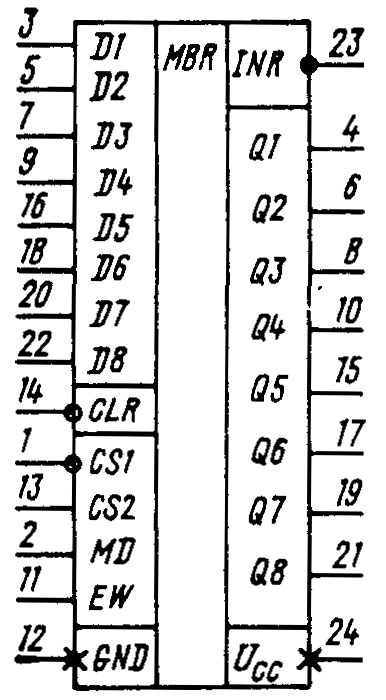

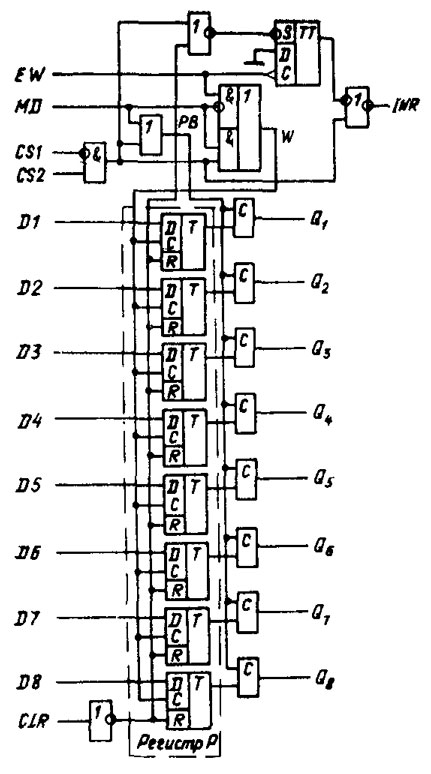

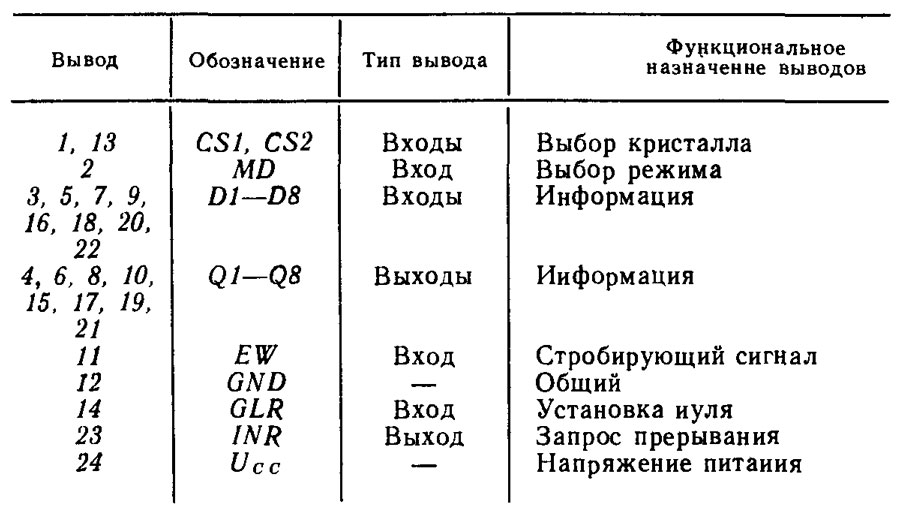

Условное графическое обозначение микросхемы приведено на рис. 11 назначение выводов— в табл. 15, структурная схема показана на рис. 12.

рис. 11 |

рис. 12 |

Таблица 15

Микросхема состоит из восьми информационных D-триггеров, восьми выходных буферных устройств с тремя устойчивыми состояниями, отдельного D-триггера для формирования запросов на прерывание и гибкой схемы управления режимами работы регистра.

Информационные D-триггеры повторяют входную информацию при высоком уровне входного сигнала MDи (CS1 - CS2) = 1, а также при EW=1 и MD=0, при низком уровне сигнала иа входе EWи (CS1 - CS2)=1 при MD=0 происходит хранение входной информации. Выходы каждого информационного триггера соединены с выходными буферными каскадами с тремя устойчивыми состояниями. Виутреиияя шина выдачи информации РВ стробирует каждый выходной буферный каскад. При наличии лог. 1 иа шине РВ выходные буферные каскады разблокированы и данные поступают иа выход соответствующей линии выходных данных (Q1—Q8). Условие выработки появления сигнала: PB=MDV CS1-CS2. Виутреиияя шина записи информации Wстробирует каждый триггер регистра. При наличии лог. 1 на шине происходит запись информации в триггер с соответствующих входных информационных шин (D1—D8). Условие появления сигнала: W=EW ٨ MDV MD-CS1*XCS2. Информация в триггерах МБР обнуляется асинхронно входным сигналом CLR.

В МБР управляющими входами являются CS1, CS2, MDи EW. Эти входы используются для управления выборкой устройства, информацией регистра, состоянием выходных буферных каскадов и триггером запроса на прерывание.

Выборкой кристалла управляют входы CS1 и CS2. При наличии лог. 0 иа входе CS1 н лог. 1 иа входе CS2 устройство выбрано. Сигнал выборки кристалла (CS1, CS2) используется как синхросигнал для асинхронной установки состояния выходных буферных каскадов регистра и триггера запроса прерывания.

Вход MD(выбор режима) определяет одни из двух режимов работы. При наличии лог. О на входе MDустройство работает в режиме ввода. В этом режиме, выходные буферные каскады открыты, когда устройство выбрано. Управление записью осуществляется сигналом по входу EW.

При наличии лог. 1 на входе MD устройство работает в режиме вывода. В этом случае выходные буферные каскады открыты независимо от выборки устройства.

Вход EW используется как синхросигнал для записи информации в регистр при MD = 0 и для синхронной установки триггера запроса прерывания.

Триггер запроса прерывания служит для выработки сигнала запроса прерывания в процессорной системе. При установке системы в исходное состояние инзким уровнем сигнала CLRтриггер запроса прерывания устанавливается в 1, т. е. данное устройство ие требует прерывания. Одновременно этим же сигналом происходит установка регистра в 0. Принято, что МБР находится в состоянии прерывания, когда выходу INRсоответствует лог. 0, что позволяет обеспечить прямое соединение с входами запроса блока приоритетного прерывания. При работе в режиме ввода (т. е. иа входе MDсигнал низкого уровня) входной сигнал EWпроизводит запись информации в регистр данных и установку триггера запроса в 0. Триггер запроса прерывания устанавливается в 1 при условии выбора устройства (также вырабатывается сигнал прерывания на выходе 1NR).

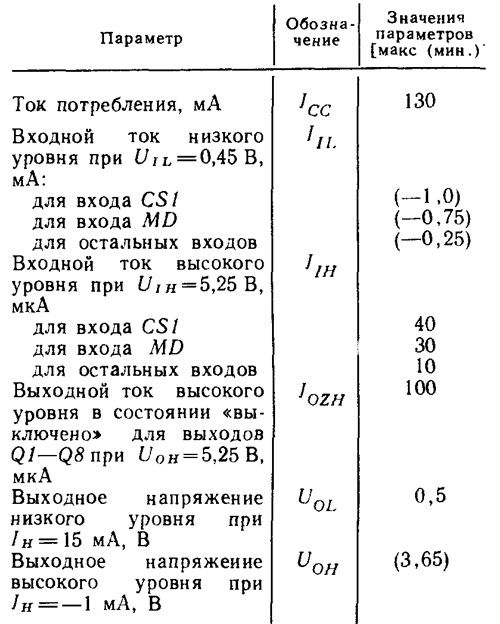

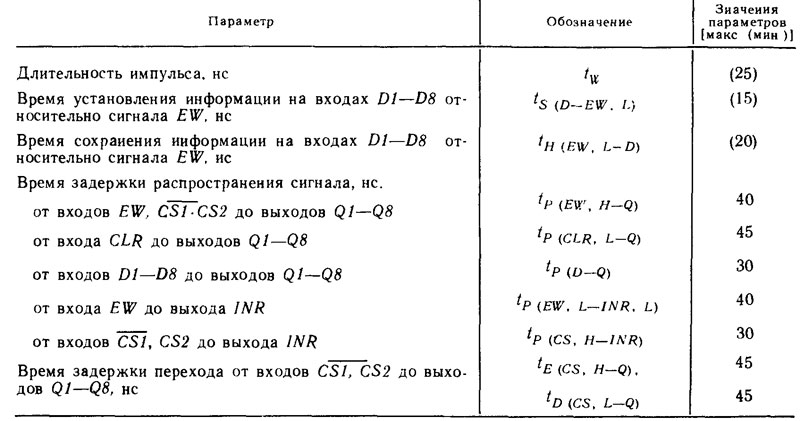

В табл. 16 и 17 — статические и динамические параметры МБР соответственно.

Таблица 16

Таблица 17

|